- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- QorIQ Processing Platforms

- :

- P-Series

- :

- Re: P2041 Serdes PLL could not work correct

P2041 Serdes PLL could not work correct

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

P2041 Serdes PLL could not work correct

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I use P2041 with LANE H as SGMII and Lane E/F as PCIE-2.

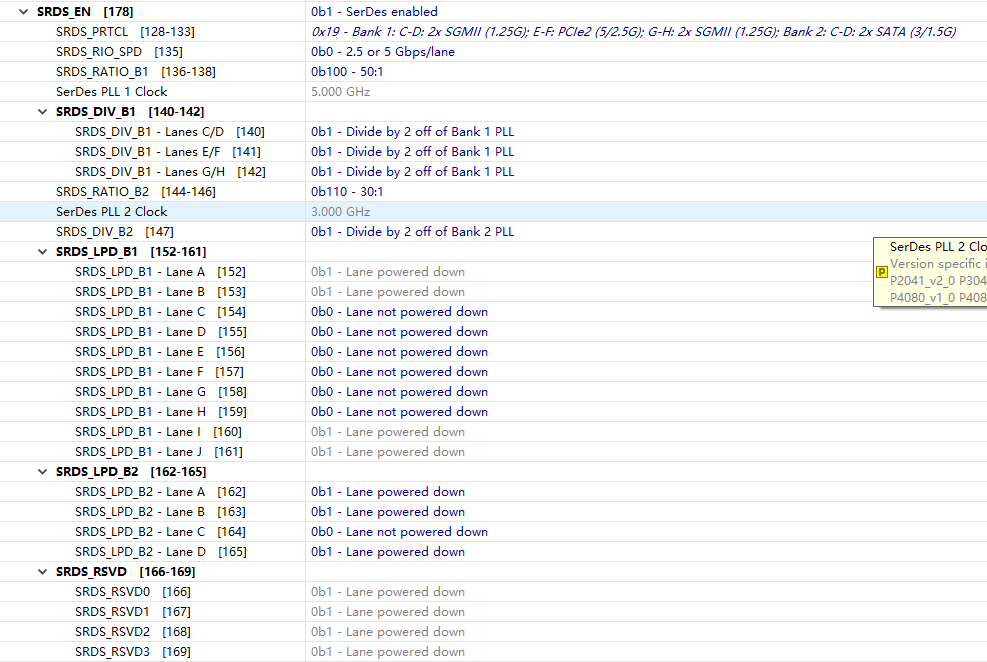

but when cpu bootup,I found SDRDS Register is as Follows:

|---B0RSTCTL = 0x26474507.

|---B1PLLCR0 = 0x0000000c.

|---B1PLLCR1 = 0x08000100.

it means that Serdes is reset failed.

follows is my RCW:

after this,i excute a reset sequence for SRDES,it out put as follows and reset failed at last:

-> serdes_reset

|---B0RSTCTL = 0x26474507.

|---B1PLLCR0 = 0x0000000c.

|---B1PLLCR1 = 0x08000100.

Set SD_RST

|---B0RSTCTL = 0x26474547.

|---B1PLLCR0 = 0x0000000c.

|---B1PLLCR1 = 0x08000100.

SET SDPD and PLLRST

|---B0RSTCTL = 0x26474567.

|---B1PLLCR0 = 0x0000000c.

|---B1PLLCR1 = 0x08000100.

SET RSTREQ

|---B0RSTCTL = 0x06474562.

|---B1PLLCR0 = 0x0000000c.

|---B1PLLCR1 = 0x08000100.

Clear SD_RST SDPD and PLLRST

|---B0RSTCTL = 0x06474504.

|---B1PLLCR0 = 0x0000000c.

|---B1PLLCR1 = 0x08000100.

value = 27 = 0x1b

-> serdes_dump

|---B0RSTCTL = 0x26474507.

|---B1PLLCR0 = 0x0000000c.

|---B1PLLCR1 = 0x08000100.

value = 27 = 0x1b

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

SD_IMP_CAL_RX has to be connected through 200 Ohm to SVDD which is 1.0V only.

Provided reference clock photos show that the scope has insufficient bandwidth - the signal looks like a sinus, but it has to be digital (with sharp edges).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

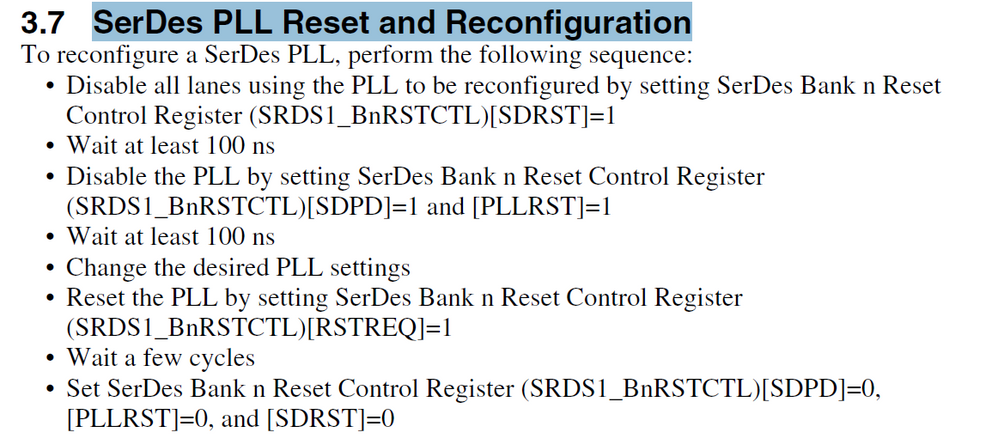

follow the P2040-RM Part 3.7:SerDes PLL Reset and Reconfiguration.

I Write the SRDS1_BnRSTCTL register and read the register(B0RSTCTL /B1PLLCR0 /B1PLLCR1 ) back

Have you programmed the RCW into a Flash?

the value of RCW is read back from flash.