- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- Other NXP Products

- :

- PTN3460IBS PWM output frequency

PTN3460IBS PWM output frequency

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

PTN3460IBS PWM output frequency

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am using a PTN3460IBS with a Q7 system on module equipped with an Intel E3845 to provide two display outputs. The primary display is connected to the dual LVDS interface of the Q7 module (sourced from an ANX1122 eDP to LVDS bridge). The second display is connected to via the PTN3460IBS configured as a dual LVDS interface. The PTN3460IBS is configured as master mode with the EDID and configuration in external EEPROM. We initially failed to get the backlight on as there was no PWM output from the PTN3460IBS. The PWM bitcount at address 0x8F was set to 0x0A and PWM frequency at address 0x92 to 0x02 to obtain a PWM frequency of approximately 13kHz. With byte locations 0x8F, 0x92 changed back to 0x0C and 0x1E as per AN11128 we generated a PWM signal of around 220Hz and after some flickering managed to drive the display briefly.

The backlight driver board we are using requires a DC signal for operation so we are using a low pass filter to derive the signal from the PWM output. The low pass filter has a 3dB cutoff of around 80Hz so we are seeing quite a bit of ripple on the backlight control signal. Can you provide guidance as to the limits of the PWM output frequency ? Is there a more detailed description of the PTN3460IBS registers other than AN11128 ? I would like to understand how to configure the device correctly to achieve the optimum solution.

Regards,

Steve Pape

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Steve,

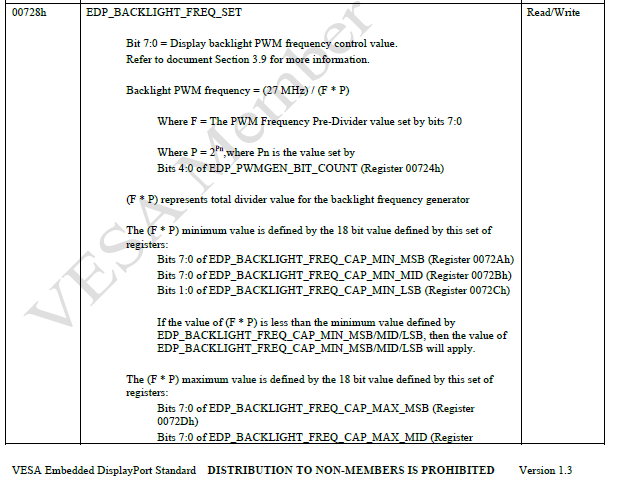

PTN3460IBS PWM output frequency registers (0x8F and 0x92) were designed as defined in eDP V1.3 specification.

Please download eDP V1.3 specification (see below figure for reference) from VESA.org for the detailed explanations. The DP specification is only for VESA members, so I cannot post it here.

Best regards,

Tomas

PS: If this answer helps to solve your question, please mark it as "Correct" or “Helpful”. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Tomas,

Thank you for the information. I have managed to get the PWM working correctly. The register description of EDP_PWMGEN_BIT_COUNT led to the solution. We had a PWM value of 0x07FF in bytes 0x90-91 which is 50% for a count value of 12 but 100% for a count value of 10. Keeping a count value of 12 ( Byte 0x8f = 0x0c) and changing the default frequency to 1 ( Byte 0x92 = 0x01) resulted in a PWM frequency of 6.59kHz which iresults in a clean dc control signal after the low pass filter.

Regards,

Steve