- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- Other NXP Products

- :

- Re: PTN3460I questions

PTN3460I questions

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

PTN3460I questions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi.

How I can get Flash-over-AUX Utility and PTN3460I DPCD utility tool and the latest firmare for PTN3460I?

And the next question is in next: we need to set the EDID with resolution 1280x1024. As far as I know there is 2 ways to do it:

1) Set the external eeprom and write to there the full table (7 EDIDs+ config bits) and start the PTN3460 with dev_cfg pin in high mode;

2) Set the need EDID in internal memory of PTN3460. And as I understand we need to configure the number of EDID, which will be emulated by PTN3460.

Correct me please if I am wrong.

And the DPCD utility have the ability to rewrite the configure bits of PTN3460 via Display Port, if I am not wrong.

Offtop: Now we have situation, when we are trying to start Ubuntu and there is 2 situations: when cfg_4 (testmode low) set to high, on bios we have correct resolution, but when system starts the maximum availible resolution is 1024x768. When cfg_4 in low position, then we have 4 bios windows in 800x480 resolution, but Ubuntu starts correct, because we are in Ubuntu emulating the correct EDID.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I cannot public the requested tools in a public space as the NXP community, but I will use your open case 00223825 to share the tools with you.

Latest hardware and firmware version is the PTN3460BS/F6Y and PTN3460IBS/F2MP.

There is no more detailed information about the Flash-over-AUX Communication other than the shown in the Application Note AN11606.

AN11606: https://www.nxp.com/docs/en/application-note/AN11606.pdf

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

And I have again some questions.

What is the correct sequence of steps whic I need to do to start PTN3460 from EXTERNAL eeprom:

a) set dev_cfg to 1 -> PTN3460 load the configuration table from eeprom and PTN will be in work mode;

b) set dev_cfg to 1 -> PTN3460 load the configuration table from eeprom -> set dev_cfg to 0 -> PTN will be in work mode?

Is there some information about the i2c eeprom adress is need to be configured to correct connection between PTN3460 and eeeprom?

What minimum size of eeprom I need so store my edid and config bits?

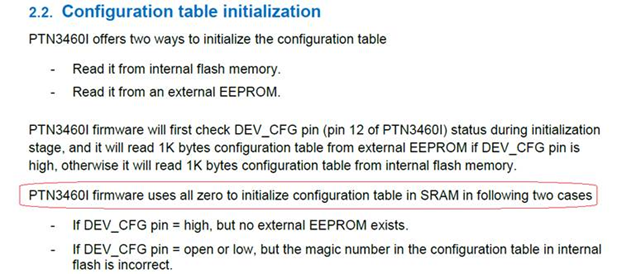

In PTN3460I Eval. Board with AUO 7" Panel Rev.1.0 sch pdf document memory is 24C02 2K bit value, but in AN11606 PTN3460I Programming Guide on page 4 sad, that "PTN3460I firmware will first check DEV_CFG pin (pin 12 of PTN3460I) status during initialization stage, and it will read 1K bytes configuration table from external EEPROM if DEV_CFG pin is high, otherwise it will read 1K bytes configuration table from internal flash memory".

I don't understand how I can start PTN with EDID what I need. I tryed to read it from external eeprom in any variations, but when I am reading it (dev_cfg high) there is no HPD signal from PTN and there is no image on lcd display. (I just put dev_cfg to high and wait while ptn will not start. Maybe I need to do next: start ptn with dev_cfg high, wait 5 seconds, make dev_cfg low and then it will be work?)

So many questions and few answers... I hope You will help me with it.

Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I used your open case 00223825 to share the tools with you. Check your case.

Answering to your questions:

What is the correct sequence of steps which I need to do to start PTN3460 from EXTERNAL eeprom:

- a) set dev_cfg to 1 -> PTN3460 load the configuration table from eeprom and PTN will be in work mode;

- b) set dev_cfg to 1 -> PTN3460 load the configuration table from eeprom -> set dev_cfg to 0 -> PTN will be in work mode?

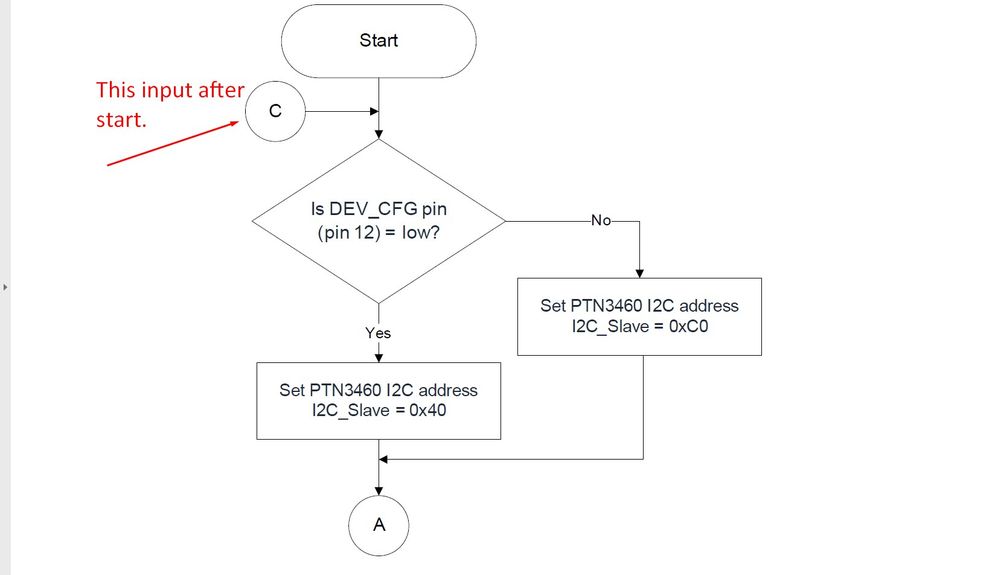

[ANSWER] PTN3460I uses configuration table in the internal SRAM for operation. When PTN3460 powers up, PTN3460I will read in DEV_CFG pin status to decide whether it will read in configuration table either from internal flash memory or external EERPOM into internal SRAM for application operation.

Is there some information about the i2c eeprom adress is need to be configured to correct connection between PTN3460 and eeeprom?

[ANSWER] PTN3460I only supports I2C salve address 0xA0 for external EEPROM.

What minimum size of eeprom I need so store my edid and config bits?

In PTN3460I Eval. Board with AUO 7" Panel Rev.1.0 sch pdf document memory is 24C02 2K bit value, but in AN11606 PTN3460I Programming Guide on page 4 sad, that "PTN3460I firmware will first check DEV_CFG pin (pin 12 of PTN3460I) status during initialization stage, and it will read 1K bytes configuration table from external EEPROM if DEV_CFG pin is high, otherwise it will read 1K bytes configuration table from internal flash memory".

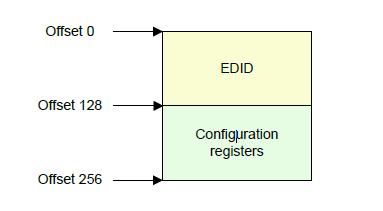

[ANSWER] PTN3460I only support 256 bytes data in external EEPROM which first 128 bytes is for EDID and second 128 bytes is for configuration registers. The first 128 bytes EDID will be stored in the EDID No 0 in the internal SRAM, and customer need to set configuration register 0x84 = 0x01 (EDID emulation is ON, EDID no 0 is selected), so that PTN3460I will use EDID No 0 in application.

I don't understand how I can start PTN with EDID what I need. I tried to read it from external eeprom in any variations, but when I am reading it (dev_cfg high) there is no HPD signal from PTN and there is no image on lcd display. (I just put dev_cfg to high and wait while ptn will not start. Maybe I need to do next: start ptn with dev_cfg high, wait 5 seconds, make dev_cfg low and then it will be work?)

[ANSWER] You need to pre-program external EEPROM if you want to use configuration table from EERPOM. And if you have empty EERPOM and DEV_CFG pin = 1, then PTN3460I will not work.

Regards,

Jose

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Alberto!

Do I understand correctly that PTN constantly looks at the dev_cfg pin and selects the table based on it. I. e. the choice of the configuration table occurs not only at the moment of inclusion? Such thoughts were prompted by the flowchart presented in the screenshot.

And it would be very good if you answered my previous questions.

Thank you!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you, Jose, for such вdetailed answers!

A will try this recomendations and will say the results!

UPD.

I tried to apply Your recomendations and none of it helped.

My steps:

I write to EEPROM EDID+CFG 256 bytes (different variations, which are atteched to this message) -> set the DEV_CFG pin to HIGH and start the board with PTN3460I.

The HPD diode is ON, but there is no image on screen. Thrue Ubuntu we are trying to get EDID, but there isn no one. In each of this EDIDROMs I trued to config the PTN thrue CFG3 & CFG4 pins, but no matter how they are set: there is no one image on screen and we cant read the EDID thrue the Ubuntu. Certainly I always power off the device, make new config and power it on again. Only one situation when we can read the EDID from PTN 3460I is when: DEV_CFG in LOW, CFG4 - LOW, CFG3 - LOW and we get the 800x480 resolution. And it is work and on Windows, and on Ubuntu, and looks like it is EDID1 from firmare.

What are we are doing wrong?

Does the AUX bus communication work when the PTN3460 is in master mode, or is it 2 independent buses and the image is missing due to incorrect EDID and configuration bits?

Do I need to set the pin configuration settings in the configuration bits (registers 0x8D & 0x8E)?

Do I need to set the CFG1-CFG4 pins when I am load the configuration table from external EEPROM?

And little questions about Panel timings (registers 0x93, 0x94, 0x97 do I understand correctly that each bit will be equal to 50ms, i.e. standart value of 0x93 -> 0x0A = 0b0000 0101 = 10*50ms = 500ms; 0x94 -> 0x14 = 0b0001 0100 = 20 * 50ms = 1000ms; 0x97 -> 0x02 = 2 * 50ms = 100 ms?

P.S.There is 1 not correct moment in my board: I dont place the capacitors in AUX lines and not pulled it up and down thrue 1 MOhm. But I think if it was not work it can't recognise any EDIDs, even 800x480, but we can run it.

I sure that together we will solve this task!=)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I checked your case with the applications engineers and they did slight modification of your EEPROM bin files at attached, please test them out to see whether they work in your application (DEV_CFG pin = 1).

About your questions, please find our comments in below:

I write to EEPROM EDID+CFG 256 bytes (different variations, which are atteched to this message) -> set the DEV_CFG pin to HIGH and start the board with PTN3460I.

The HPD diode is ON, but there is no image on screen. Thrue Ubuntu we are trying to get EDID, but there isn no one. In each of this EDIDROMs I trued to config the PTN thrue CFG3 & CFG4 pins, but no matter how they are set: there is no one image on screen and we cant read the EDID thrue the Ubuntu. Certainly I always power off the device, make new config and power it on again. Only one situation when we can read the EDID from PTN 3460I is when: DEV_CFG in LOW, CFG4 - LOW, CFG3 - LOW and we get the 800x480 resolution. And it is work and on Windows, and on Ubuntu, and looks like it is EDID1 from firmare.

ANSWER>

It is a good sign which proves that PTN3460I board working properly while DDEV_CFG pin is set to low (not using external EERPOM condition).

What are we are doing wrong?

Does the AUX bus communication work when the PTN3460 is in master mode, or is it 2 independent buses and the image is missing due to incorrect EDID and configuration bits?

ANSWER>

AUX bus communication works when the PTN3460 is in master mode, but AUX bus communication may fail if there are incorrect EDID and configuration bits settings in the EEPROM (configuration table).

Do I need to set the pin configuration settings in the configuration bits (registers 0x8D & 0x8E)?

ANSWER>

You only set pin configuration settings when you need to those functions.

Do I need to set the CFG1-CFG4 pins when I am load the configuration table from external EEPROM?

ANSWER>

Yes and no. When PTN3460I powers up, it will read configuration table into internal SRAM either from internal flash memory (if DEV_CFG pin = open or low) or external EEPROM (if DEV_CFG pin = high), then it will check configuration register 0x8E bits setting, and if corresponding bit = 0, then it read in CFG (1-4) pin status to overwrite the setting in the configuration table (in internal SRAM). And if corresponding bit = 1, then PTN3460I will keep configuration table no changes (doesn’t read in CFG pins status to overwrite configuration table settings).

And little questions about Panel timings (registers 0x93, 0x94, 0x97 do I understand correctly that each bit will be equal to 50ms, i.e. standart value of 0x93 -> 0x0A = 0b0000 0101 = 10*50ms = 500ms; 0x94 -> 0x14 = 0b0001 0100 = 20 * 50ms = 1000ms; 0x97 -> 0x02 = 2 * 50ms = 100 ms?

ANSWER>

Yes, it is correct.

P.S. There is 1 not correct moment in my board: I dont place the capacitors in AUX lines and not pulled it up and down thrue 1 MOhm. But I think if it was not work it can't recognise any EDIDs, even 800x480, but we can run it.

ANSWER>

It may work but it’s no good for signal quality point of view. The A/C cap is used to isolate DC level between transmitter and receiver and two 1 Mohm resistors are used to for AUX channel connection/disconnection detection.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello!

Thank you for your so fast answer! You are amazing!

Where I can find firmwares PTN3460BS/F6Y and PTN3460IBS/F2MP?

Can I download this firmwares thrue DPCD tool or FoA Utility?