- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Topics

- :

- NXP Designs

- :

- Does K32L2B31VFM0A/K32L2 include multiplier or not?

Does K32L2B31VFM0A/K32L2 include multiplier or not?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Does K32L2B31VFM0A/K32L2 include multiplier or not?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1) K32L2B3xRM.pdf, page 51, $3.1: "The processor supports the ARMv6-M instruction set (Thumb) architecture including all but three 16-bit Thumb opcodes (52 total) plus seven 32-bit instructions." Could you please show us these detail three 16-bit Thumb opcodes (52 total) plus seven 32-bit instructions? K32L2B31VFM0A, does this chip include multiplier or not?

2) DDI0484C_cortex_m0p_r0p1_trm.pdf, page1-5, $1.4.1 Configurable multiplier, "The MULS instruction provides a 32-bit x 32-bit multiply that returns the least-significant 32-bits of the result. The processor can implement MULS in one of two ways: As a fast single-cycle array. As a 32-cycle iterative multiplier." If yes, for K32L2B31VFM0A, "a single-cycle multiplier, in designs optimized for high performance" or "a 32-cycle multiplier, in designs optimized for low area", which one is inside this chip?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jack xiang,

1. K32L2B3xRM.pdf, page 51, $3.1: "The processor supports the ARMv6-M instruction set (Thumb) architecture including all but three 16-bit Thumb opcodes (52 total) plus seven 32-bit instructions." Could you please show us these detail three 16-bit Thumb opcodes (52 total) plus seven 32-bit instructions? K32L2B31VFM0A, does this chip include multiplier or not?

Answer:

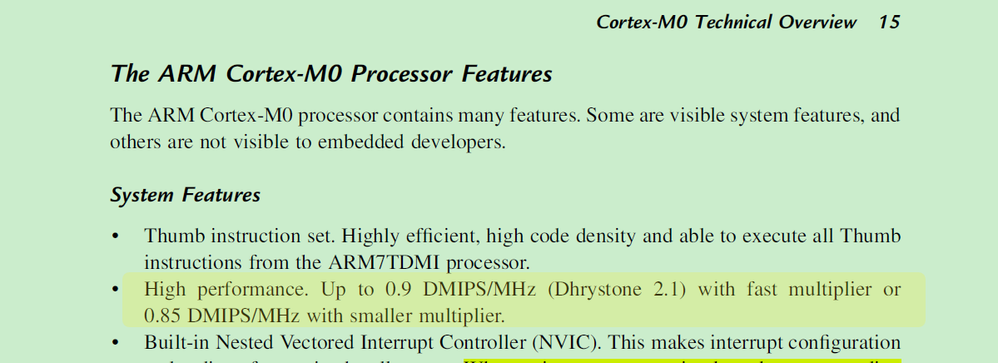

K32L2B3x is the ARM Cortex M0+ core, from the ARM core document, you can know, the ARM Cortex M0+ core can support the multiplier:

The following picture is from :The Definitive Guide to the ARM Cortex-M0

About the related instructions, you can check the asm code, this is the KE series with the same Cortex M0+ core:

The instructions is muls

2) DDI0484C_cortex_m0p_r0p1_trm.pdf, page1-5, $1.4.1 Configurable multiplier, "The MULS instruction provides a 32-bit x 32-bit multiply that returns the least-significant 32-bits of the result. The processor can implement MULS in one of two ways: As a fast single-cycle array. As a 32-cycle iterative multiplier." If yes, for K32L2B31VFM0A, "a single-cycle multiplier, in designs optimized for high performance" or "a 32-cycle multiplier, in designs optimized for low area", which one is inside this chip?

Answer: It should be the faster multiplier with single-cycle multiplier,

This post may also useful to you.

Use of Cortex-M0/M0+ multiply instructions on LPC43xx and LPC5410x

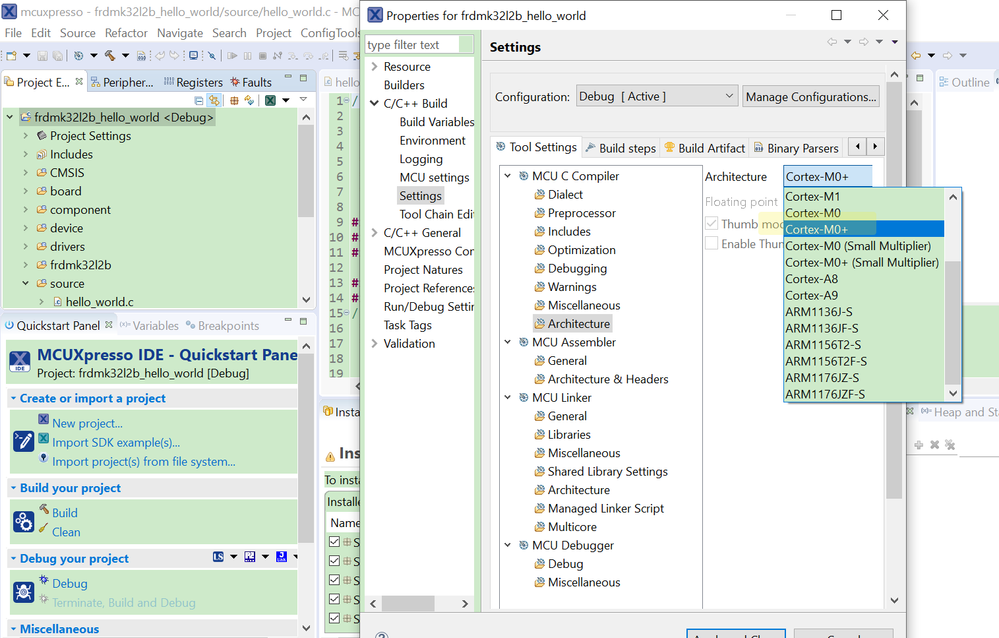

I also checked the K32L2B3 SDK, which can be downloaded from this link:

Welcome | MCUXpresso SDK Builder

You can find the MCU C Complier, architecture select Cortex M0+, not the cortex M0+ small Multiplier with 32 cycles to execute a MULS instruction.

Wish it helps you!

If you still have questions about it, please kindly let me know.

Best Regards,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------