- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Motor Control and Smart Energy

- :

- Hall Sensor XOR

Hall Sensor XOR

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Hall Sensor XOR

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

In the KV31F sub-family reference manual, there's a handy note regarding using the two 2-CH FTM modules (FTM1 and FTM2) in input capture mode for hall sensor decoding. Apparently one of the SIM_SOPT4 register bits controls the input to FTM2 CH1. If the three hall sensors are connected to FTM1 CH0, FTM1 CH1, and FTM2 CH0 then setting this bit appropriately will result in the "Exclusive-OR" of the three hall sensor lines which could result in reduced complexity in calculation.

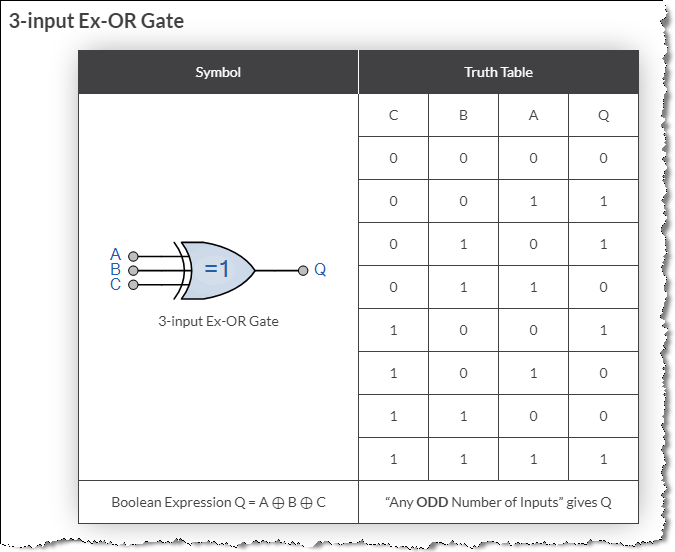

My question is regarding the interpretation of "Exclusive OR" for 3 signals, as there are typically two interpretations. Is this an "Only 1" (xor output is true only if only one input is true) or an "odd parity" (xor output is true if an odd number of inputs are true) interpretation?

Thanks,

Eric

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

We are using KV31 Hall_XOR how to hall sensor signals read in FTM1,FTM2 reference manual

based we are configured and that is not proper working in our configuration code bellow if any changes and missing registers

void InitFTM1(void)

{

/* enable clock to FTM module */

// SIM->SCGC6 |= SIM_SCGC6_FTM1_MASK;

FTM1->MODE = FTM_MODE_WPDIS_MASK | FTM_MODE_FTMEN_MASK;

FTM1->SC = FTM_SC_PS(4) | FTM_SC_CLKS(1) | FTM_SC_TOIE_MASK;

FTM1->CONF = FTM_CONF_BDMMODE(3);

FTM1->MOD = 0xFFFF;

FTM1->CNTIN = 0x0;

FTM1->CONTROLS[1].CnSC |= FTM_CnSC_ELSA_MASK | FTM_CnSC_ELSB_MASK;

FTM1->PWMLOAD = FTM_PWMLOAD_LDOK_MASK;

EnableIRQ(FTM1_IRQn);

}

void InitFTM2(void)

{

SIM->SCGC6 |= SIM_SCGC6_FTM2_MASK|SIM_SCGC6_FTM1_MASK;

SIM->SOPT4 |= SIM_SOPT4_FTM2CH1SRC_MASK;

FTM2->MODE |= FTM_MODE_FTMEN_MASK;

FTM2->CONF |= FTM_CONF_BDMMODE(3);

FTM2->MOD = 0xFFFF;

FTM2->CNTIN = 0;

FTM2->SC |= FTM_SC_CLKS(1);

FTM2->SC |= FTM_SC_PS(7);

FTM2->CONTROLS[0].CnSC |= FTM_CnSC_ELSA_MASK | FTM_CnSC_ELSB_MASK;

FTM2->CONTROLS[1].CnSC |= FTM_CnSC_ELSA_MASK | FTM_CnSC_ELSB_MASK | FTM_CnSC_ICRST_MASK;

FTM2->CONTROLS[1].CnSC |= FTM_CnSC_CHIE_MASK;

EnableIRQ(FTM2_IRQn);

}

BR

PANDI

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Eric,

I think it's an "odd parity" (xor output is true if an odd number of inputs are true). You can have a try to test it.

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------