- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- 基于模型的设计工具箱(MBDT)

- :

- 基于模型的设计工具箱(MBDT)

- :

- How are Message Buffers allocated among multiple CAN buses on MPC57xx?

How are Message Buffers allocated among multiple CAN buses on MPC57xx?

If multiple CAN buses are utilized on a MPC57xx with Rx FIFO how are the Message Buffers (MBs) distributed amongst the CAN buses? Also, which MB numbers are available for Tx?

In the simple case where a single CAN bus is used, MBs 0 through 5 are reserved by FIFO. Also additional consecutive MBs are reserved equal to the count of elements in the Rx FIFO Filter Table. The remaining higher numbered MBs are available for CAN Tx. This is explained in the documentation for the FCAN Configuration Block.The documentation is not clear on how the MBs are distributed when multiple CAN buses are implemented.

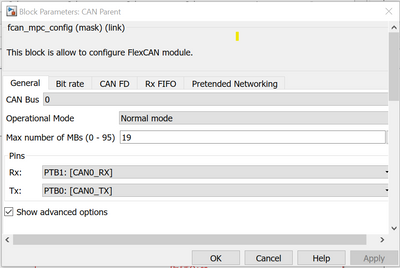

I have a CAN gateway that consists of DEVKIT-MPC5748G and DEVKIT-COMM. I make use of 5 CAN buses. 96 MBs are available. In each of the 5 CAN configuration blocks I have reserved 19 MBs as shown.

-- Have I allocated the MBs in the best way so I have access to all MBs?

-- Which MB numbers are reserved by each CAN Bus for Rx FIFO?

-- Which MB numbers are available to each CAN bus for Tx?

-- Are the MBs available for Tx shared amongst the 5 CAN buses?

已解决! 转到解答。

Hi @ranulf ,

On MPC5748G each FlexCAN module includes 96 message buffers (MBs). FlexCAN0 has 96 MBs, FlexCAN1 another 96 MBs, and so on. The MBs are not shared between the CAN buses.

When the Rx FIFO is enabled, MBs 0–5 are used by the Rx FIFO engine.

An additional memory area occupied by MBs 6–37 depending on the Number Of Rx FIFO Filters setting, contains the ID filter table (configurable from 8 to 128 table elements) that specifies filtering criteria for accepting frames into the FIFO.

Regards,

Paul

Hi @ranulf ,

On MPC5748G each FlexCAN module includes 96 message buffers (MBs). FlexCAN0 has 96 MBs, FlexCAN1 another 96 MBs, and so on. The MBs are not shared between the CAN buses.

When the Rx FIFO is enabled, MBs 0–5 are used by the Rx FIFO engine.

An additional memory area occupied by MBs 6–37 depending on the Number Of Rx FIFO Filters setting, contains the ID filter table (configurable from 8 to 128 table elements) that specifies filtering criteria for accepting frames into the FIFO.

Regards,

Paul