- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

Hi,

I've tested the SDCLK and noticed it works default in 20MHz clock, so i've managed to chage it to 40MHz but not to 50MHz.

My code looks like that:

/* Set SDCLK to 40Mhz*/

esdhc_ptr->SYSCTL &= 0xFFFFFFF7; //Disable the SD Clock

esdhc_ptr->SYSCTL &= 0xFFFF00FF; //Setting the Prescaler to 0

esdhc_ptr->SYSCTL |= 0x00000020; //Setting the Divisor to 3

esdhc_ptr->SYSCTL |= 0x00000008; //Enable the SD Clock

esdhc_ptr->SYSCTL |= 0x00000004; //Remain the SDHC clock always enabled

已解决! 转到解答。

Hello,

SIM_SOPT2[SDHCSRC] register specifies Clock for SDHC peripheral. I note that you did not clarify your target MCU, therefore everything what I have written is for K40. Slight changes might be for different MCU.

Regards,

MartinK

Hello,

SIM_SOPT2[SDHCSRC] register specifies Clock for SDHC peripheral. I note that you did not clarify your target MCU, therefore everything what I have written is for K40. Slight changes might be for different MCU.

Regards,

MartinK

Again, Thank you for your true help! :smileyhappy:

I forgot to mention my MCU: K60F120M, if there is any change to what you wrote i will be happy to know :smileyhappy:

Sincerely yours,

Naftali.

Hi Markku!

Thank you for your help.

I did managed to get 50MHz with the source of the OSC0ERCLK:

/* My Code for this is: */

SDHC_MemMapPtr esdhc_ptr = SDHC_BASE_PTR;

SIM_MemMapPtr sim_ptr = (SIM_MemMapPtr)0x40047000; //Base address of the SIM

/* Set the SDHC clk source to OSC0 = 50MHz */

sim_ptr->SOPT2 |= 0x20000000; //Set ESDHCSRC clk to OSC0ERCLK

esdhc_ptr->SYSCTL &= 0xFFFF00FF; //Disable the Prescaler

esdhc_ptr->SYSCTL &= 0xFFFFFF0F; //Disable the Divisor

Thank you all for your help: Kojto and Markku!!

:smileyhappy:

Hello naftalir,

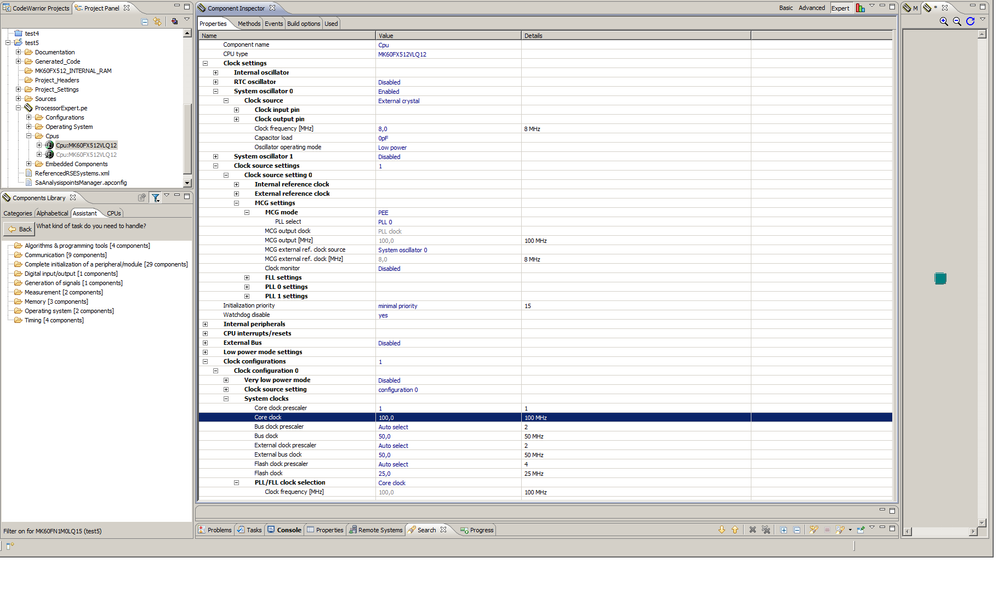

I assume you are using Kinetis platform. There''s section in Reference Manual for your MCU where this equation is written:

Clock frequency = Base clock / (prescaler x divisor)

There's not much to do here to set desired 50 MHz with 120 MHz source clock. Closest you can get is 40 MHz. You can anyway change the bus clock.

Regards,

MartinK

Hello,

I forgot to mention, there's chapter in Reference manual dedicated to Clock distribution with the same name.

This is based on Kinetis 40: There're 4 possible clock sources :

System clock

MCGPPLLCLK/MCGFLLCLK

OSCERCLK

SDHC0_CLKIN

You can select one of these clock sources for SDHC module and customize divider to have 50 MHz.

Regards,

MartinK