- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Processor Master ID

Processor Master ID

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Processor Master ID

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

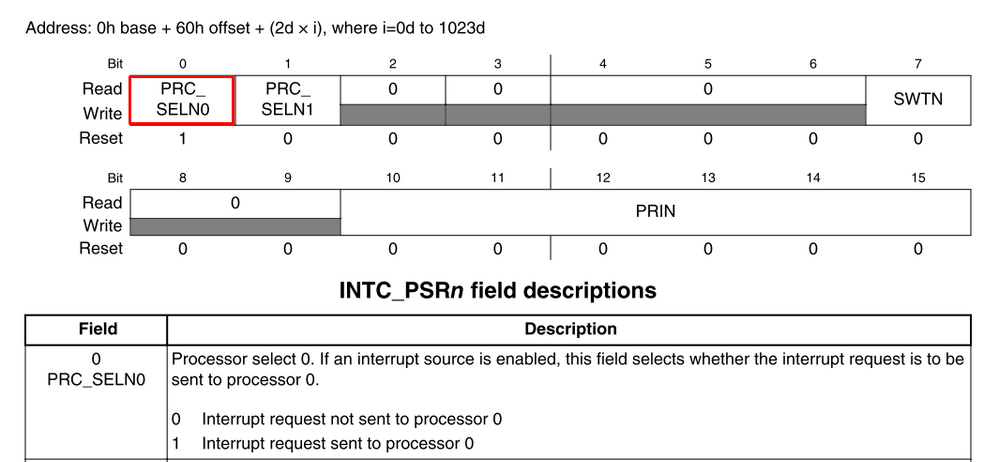

In the Reference Manual for MPC574x Power PC, interrupts section, there is frequent reference to Processor Master ID as in this description for the PSRn register configuration:

"

Only the processor with master ID zero will be allowed to write the INTC_PSRn[PRC_SEL,SWT]. When writing the INTC_PSR[PRI], only the processor with master ID 0 and the processor who’s master ID matches the setting of the

INTC_PSRn[PRC_SEL] will be allowed to write the INTC_PSRn[PRI]. An attempt by any other processor to write the PSRn[PRIn] will result in a termination error.

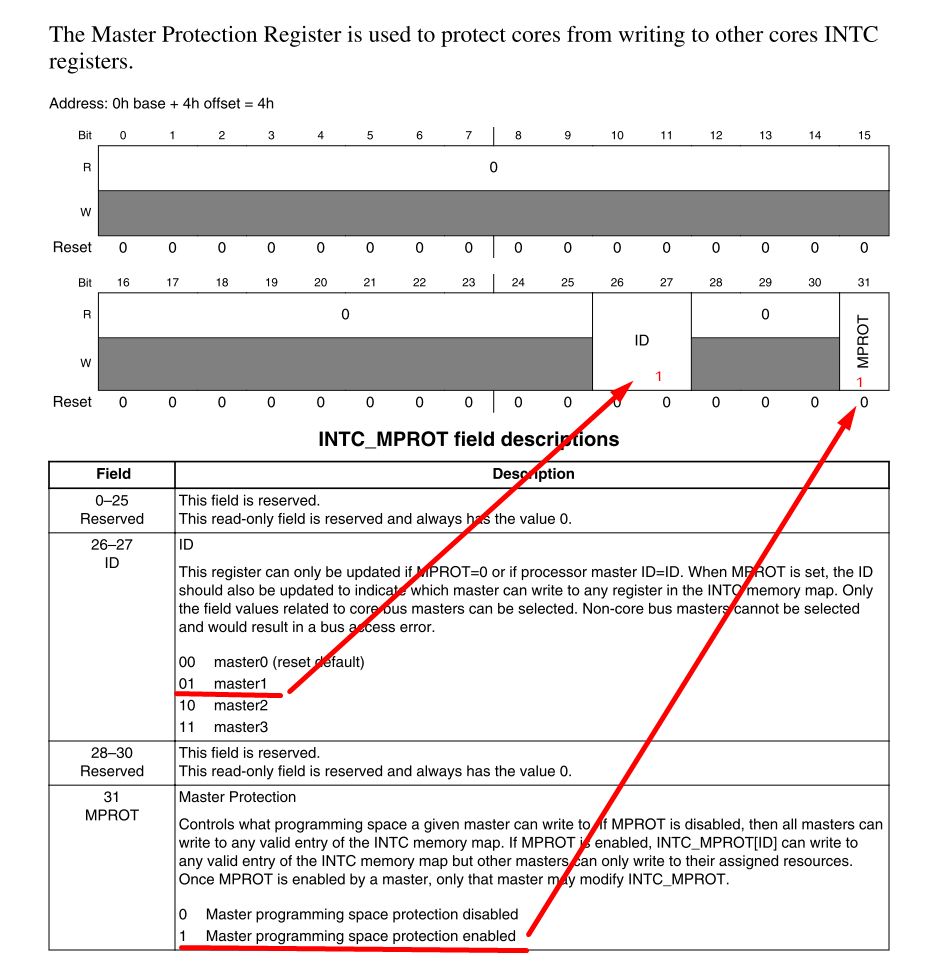

If INTC_MPROT[MPROT]=0 (disabled), all processors have write access.

If INTC_MPROT[MPROT]=1 (enabled), the processor with master ID (0-3) = INTC_MPROT[ID] or the corresponding processor has write access to INTC_PSRn[PRC_SEL,SWT], otherwise, a termination error is asserted. When writing

the INTC_PSRn[PRI], only the processor with master ID (0-3) = INTC_MPROT[ID] and the processor whose master ID (0-3) matches the setting of the INTC_PSRn[PRC_SEL] will be allowed to write the INTC_PSRn[PRI]. An attempt by any other processor to write the INTC_PSRn[PRI] will result in a termination error.

"

For all other configuration, I use the coreId of 0 to n-1 (n = number of cores) to split the processing between the cores. (a) What is master ID? is it different from coreId? Is it configurable by the user?

(b ) what does "corresponding processor" mean in the above description?

(c) In S32DS, how can I configure MPROT and MPROT_ID using Processor Expert?

(d) For my application, i want to use Software interrupt SS5_IRQn to interrupt core1 from core0. Only core0 should be able to set the interrupt and only core 1 should be able to clear the interrupt. How should the register be configured?

Thank you.

JoyR

@Alex_Peck

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

(a) What is master ID? is it different from coreId? Is it configurable by the user?

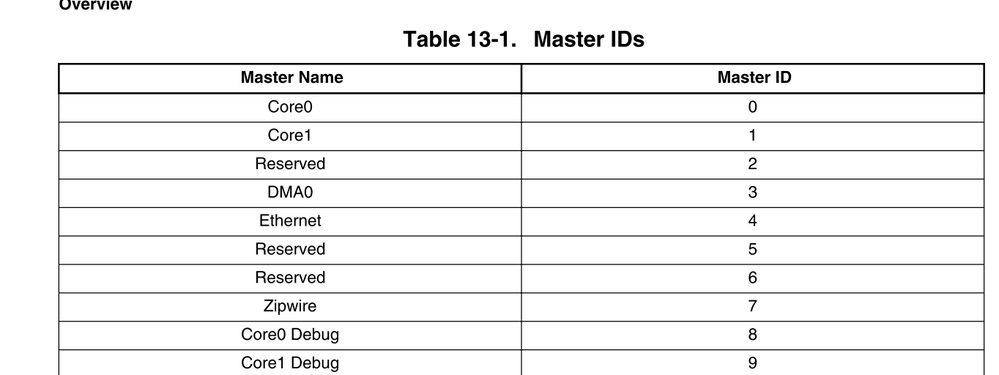

Master ID => is the logical bus master assignments

As I do not know which device you are using I can only show below the screenshot of MPC5746R reference manual.

(b ) what does "corresponding processor" mean in the above description?

Means only processor which ID corresponds to INTC_MPROT access settings.

(c) In S32DS, how can I configure MPROT and MPROT_ID using Processor Expert?

I am not familiar with PExpert. Someone else should answer you quesiton.

(d) For my application, i want to use Software interrupt SS5_IRQn to interrupt core1 from core0. Only core0 should be able to set the interrupt and only core 1 should be able to clear the interrupt. How should the register be configured?

1) Program INTC_PSR5 for core0 interrupt execution only.

This is done by default from reset settings

2) Program INTC Master Protection Register (INTC_MPROT) according to your needs

regards,

Peter