- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

MPC5777c SPI master receiving messages with using interrupt

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi there,

I'm using MPC5777c dev board, and working on SPI communication with using interrupts. MCU adjusted as Master, and it can communicate with a slave. Problem is about receiving operation.

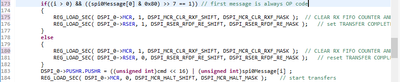

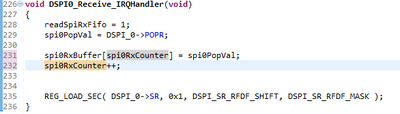

When I read a information from the slave I must send a OP code and a few dummy messages. The Dummy messages is for generating SCK. I use RFDF and TCF to generate interrupt. My aim, enable RFDF_EN bit only when dummy messages sent. I created an algorithm to do that. If OP code is about reading operation, and next message to be sent dummy, enable RFDF_EN, else disable RFDF. also I clear the RX fifo in every condition.This conditions is before the writing message to PUSH register of SPI. The Problem is I always read an zero message before actual message(s). there are a few screen shots from my code and debug. How Can I fix this issue?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

so within a TCF interrupt you halt transfer, flush RXFIFO, enable/disable RX ISR, store new word into PUSHR, start transfer. And RFDF ISR just reads RXFIFO value. This looks little bit complicated.

You can try to have RFDF ISR still enabled, so read every word. Then use TFFF to fill TXFIFO. Enable TFFF interrupt when transfer should be started, within TFFF ISR load PUSHR, before last word in frame disable TFFF ISR

BTW what is a baudrate and transfer format?

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

hi, @PetrS

firstly thanks for response. according to my settings boudrate is about 3kbps. this is not final boudrate to be used. when I get stable communication I will set boudrate to faster one. also core clock frequency is 100MHz, per_clock is 40MHz, and FM_PER_CLK is 100MHz

In every SPI frame I'm sending 8 bit. but messages occur from different number of byte.( 1,2,4,5, and 33 byte including OPCODE)

I have already tried similar algorithm to your advice, with using TFFF, EOQF, RFDF. TFFF is used for sending messages which size is larger than 4. for smaller than 4 byte I did not enable the TFFF_EN. EOQF is used for sending next message and RFDF for receiving. But opitimum design is implemented using TCF and RFDF. My problem is not complexity, the problem is receiving unexpected zeros even through RXFIFO flushed and RFDF just enabled.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

what if FIFO is disabled at all?

Or you can try to add DMA if it is applicable for application.

BR, Petr