- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- MPC5777C eTPU channel interrupt generation

MPC5777C eTPU channel interrupt generation

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MPC5777C eTPU channel interrupt generation

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am not able to generate eTPU channel interrupt for every 40ms when QOM loaded with counts corresponding to 40ms

Please refer the following settings done in

a) main.c

/* initialize pads */

SIU.PCR[ETPUB0_pin].R = (ALT1 | OBE | WPE | WPS | DRV) ;

SIU.PCR[ETPUB1_pin].R = (ALT1 | IBE | WPE | WPS | DRV) ;

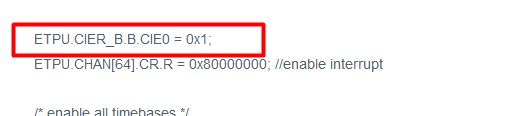

ETPU.CIER_B.B.CIE0 = 0x1;

ETPU.CHAN[64].CR.R = 0x80000000; //enable interrupt

/* enable all timebases */

fs_timer_start ();

*upper_QOM_SCR16 = 0xC0C0; /* clear QOM DMA/interrupt service request */

*upper_FPM_SCR16 = 0xC0C0; /* clear FPM DMA/interrupt service request */

/* initialize eTPU channels */

// init QOM channel Low using QOM function

// init QOM channel Low using QOM function

error_code = fs_etpu_qom_init (QOM0,

FS_ETPU_PRIORITY_MIDDLE,

FS_ETPU_QOM_SINGLE_SHOT ,

FS_ETPU_TCR1,

FS_ETPU_QOM_INIT_PIN_LOW,

FS_ETPU_QOM_IMMEDIATE,

(uint32_t *) 0,

10,

QOMLO_array_size,

my_event_array_QOMA);//my_event_array_QOMLO

/* wait for QOM to finish */

while (ETPU.CHAN[QOM0].SCR.B.CIS == 0) {};

*upper_QOM_SCR16 = 0xC0C0; // clear DMA/interrupt service request

b) MPC5777C_IsrVecTab.c

IntcIsrVectorTable:

ISRline eTPU_B0_ISR ;Vec 243,

c) Interrupts.c

void Interrupts_init(void)

{

/* Initialize INTC for software vector mode */

INTC.MCR.R = 0x00000000;

/* configure IVPR and IVORx offsets, also includes a trap for all core

exceptions, excluding IVOR4 exceptions which have seperate handler */

e200zX_Interrupt_Setup();

/* Set INTC ISR vector table base address */

INTC.IACKR.R = (uint32_t) &IntcIsrVectorTable[0];

INTC.IACKR_PRC1.R = (uint32_t) &IntcIsrVectorTable[0];

/* assing required peripheral priorities */

INTC.PSR[244].R = PRC_SEL_CPU0 | PRC_PRI(1); // eTPU_B_chnl_1

/* assing required peripheral priorities */

INTC.PSR[243].R = PRC_SEL_CPU0 | PRC_PRI(1); // eTPU_B_chnl_0

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, I am not sure what's the definition shown in your code

but in fact there two registers

eTPU_GCR_CIER_ENG1

eTPU_GCR_CIER_ENG2

in your case you need write the second one

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have set the value to register eTPU_GCR_CIER_ENG2 through ETPU.CIER_B.B.CIE0 = 0x1 and we observed that when loaded QOM time has elapsed then ETPU.CHAN[QOM0].SCR.B.CIS is set to 1 (eTPU_GCR_CISR_ENG2[CIS0] = 1) but ISR mapped to this channel has not executed

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Do you have enabled interrupts globally? Other interrupt sources works for you?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

Possible can you share any example with eTPU ISR enabled.?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

For instance you may see eTPU interrupt used in the code. It is working fine.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I tried as per the example code and its working now

Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Interrupts are enabled globally. Other interrupts like "Periodic Interrupt Timer Interrupt 0(Vector 301) and eSCI (vector 146) "are working in same workspace. In ETPU after QOM executes ETPU.CHAN[QOM0].SCR.B.CIS this bit is set after given time elapsed but its not coming to ISR handler like PIT and eSCI.