- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Re: MPC5777C EQADC configuration

MPC5777C EQADC configuration

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MPC5777C EQADC configuration

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, I am trying to initalise EQADC0 in MPC5777C controller.

How do I configure EQADC.CFPR register with below configuration

/* Send CFIFO 0 a ADC0 configuration command */

/* enable ADC0 & sets prescaler= divide by 10 */

In the datasheet EQADC.CFPR register does not have register bitwise e4xplanation.

Can someone help on configuraing CFPR register.

Thanks

Vrushali

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have a confusion on using CFPR and RFPR register.

How to decide when to use CFPR[0] CFPR[1] CFPR[2]... and same for RFPR[0]. RFPR[1].

Here is my implementation is this correct

EQADC_A.CFPR[0].R = 0x00000000 | (ANA12_TO_ADC_IA1<<8) ;

EQADC_A.CFPR[0].R = 0x00100000 | (ANA21_TO_ADC_DCLINK1_LK<<8) ;

EQADC_A.CFPR[0].R = 0x80200000 | (ANA6_TO_ADC_DCLINK1_V<<8) ;

EQADC_A.CFPR[1].R = 0x00000000 | (ANA34_TO_ADC_INV1_TA <<8) | (1 << 24); //1 is calibration value

EQADC_A.CFPR[1].R = 0x00100000 | (ANA35_TO_ADC_INV1_TB <<8) | (1 << 24); //1 is calibration value

EQADC_A.CFPR[1].R = 0x00200000 | (ANA36_TO_ADC_INV1_TD <<8) | (1 << 24); //1 is calibration value

EQADC_A.CFPR[1].R = 0x80300000 | (ANA37_TO_ADC_INV1_TC <<8) | (1 << 24); //1 is calibration value

Thanks

Vrushali

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

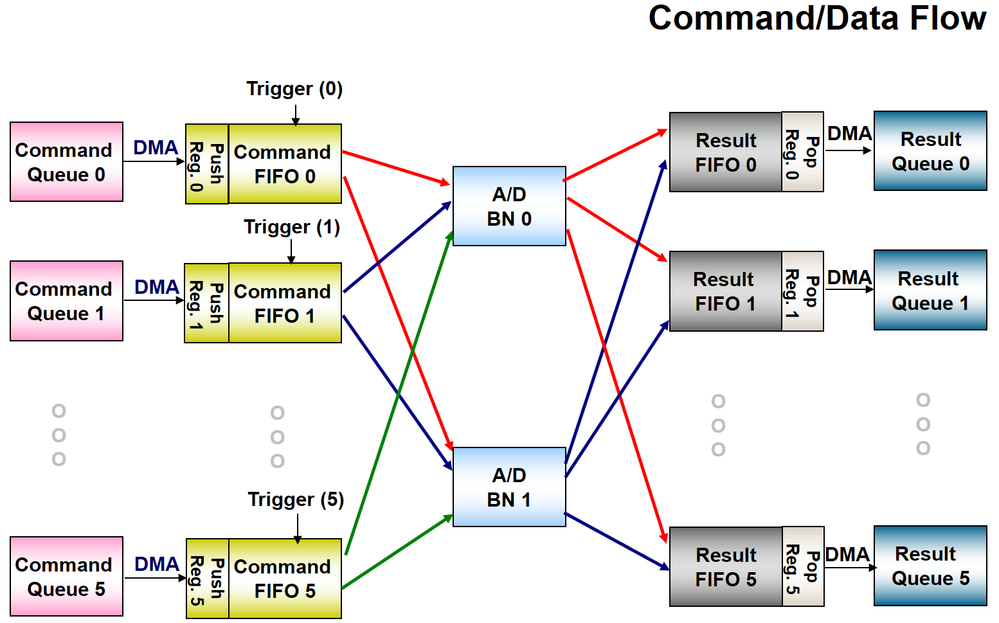

CFPRx/RFPRx chooses particular Command/Result FIFO number. Lower FIFO number has higher priority when priority processing is necessary.

Choosing of FIFO is completely up to you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks David.

I have 10 analog channels to convert, and we have 6 RFIFO, can you suggest how can we convert all 10 channels in one function itself.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Also you could pay attention to short bulletin I have written:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

Do you have example of document eQADC - avoiding unintended result swap ?

Have you implemented the solutions? I am looking for 4th solution proposed

4) To keep regular alternating of commands assigned to ADC0 and ADC1.

Thanks

Vrushali

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

How I said it is completely application dependent. If you only need to convert 10 channels in sequence, you can just use only CFIFO0 and RFIFO0, for instance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

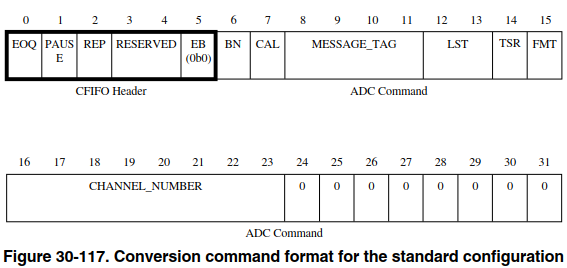

It is register for writing commands to CFIFO either due to conversion command in standard or alternate configuration or for indirect access to On-Chip ADC registers.

I could recommend you to see following example codes:

Example MPC5674F eQADC+eDMA Single_Scan CW210

Example MPC5674F eQADC+eDMA Continuous_Scan CW210

Example MPC5644A eQADC channel 146 conversion+calibration CW210

Also I am attaching header file that could be possibly useful for you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David, do you have a C file where you have used this eqadc_mamcros_Mamba.h file

Thanks

Vrushali

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have used it in this example:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks David.

I implemented same way.

However my requirement is, I have to use

22 channels of EQADCA and 7 channels of EQADC B

How do I modular the code so that for every channel configuration same function is called always.

Also need clarification when to use CFPR[0] and CFPR[1] etc and likewise CFCR0 and CRFR1 registers etc.

Here is my init and send and receive functions.

void eqadc_init (struct EQADC_tag *my_eqadc)

{

/* CBuffer0 */

my_eqadc->CFPR[0].R = B0 | MESSAGE_TAG(NULL_M) | LST(CYCLES_2) | CHANNEL(4);

my_eqadc->CFPR[0].R = EOQ | B1 | MESSAGE_TAG(NULL_M) | LST(CYCLES_2) | CHANNEL(4);

/*Trigger CFIFO 0 using Single Scan SW mode */

my_eqadc->CFCR0.R= SINGLE_SCAN_ENABLE | MODEx(SOFTWARE_TRIGGER_SINGLE_SCAN);

/*Wait for End Of Queue flag*/

while(my_eqadc->FISR[0].B.EOQFX != 1) {}

my_eqadc->FISR[0].R = End_of_Queue_Flag;

}

void SendConvCmd(struct EQADC_tag *my_eqadc, int channelnum)

{

/* Conversion command: convert channel 5 */

/* with ADC0, set EOQ */

my_eqadc->CFPR[0].R = EOQ | channelnum<<8;

}

void ReadResult(struct EQADC_tag *my_eqadc, int *Result)

{

while(my_eqadc->FISR[0].B.RFDFX != 1){}; /* Wait for RFIFO 0's Drain Flag to set */

Result = my_eqadc->RFPR[0].R; /* ADC result */

//ResultInMv = (vuint32_t)((5000*Result)/0x3FFC);

my_eqadc->FISR[0].R = RFIFO_Drain_Flag; /* Clear RFIFO 0's Drain Flag */

}

From main function I am calling it as below

eqadc_init(&EQADC_A);

eqadc_init(&EQADC_B);

SendConvCmd(&EQADC_A, 4); // here 4 corresponds to channel no 4

ReadResult(&EQADC_A, &duty);