- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Re: MPC5746C: SWT0 Reset

MPC5746C: SWT0 Reset

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MPC5746C: SWT0 Reset

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

My questions are regarding SWT0 reset type for MPC5746C

Questions:

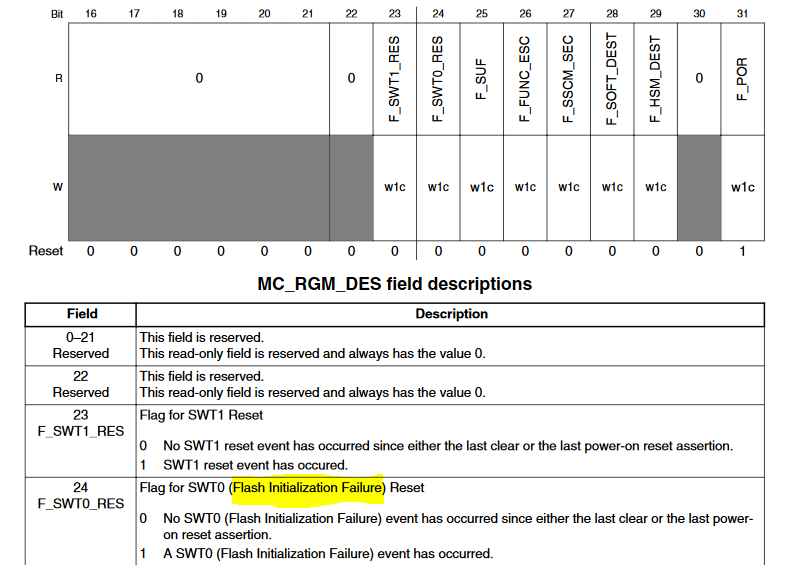

1. When the bit F_SWT0_RES is set after reset does it mean there was a Flash Initialization failure every time?

2. Will the bit F_SWT0_RES set if the reset occurs because watchdog was not refreshed? meaning no Flash Initialization failure.

3. Is there a way to trigger a functional reset when Watchdog is not refreshed?

Thank you!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

1. When the bit F_SWT0_RES is set after reset does it mean there was a Flash Initialization failure every time?

After which reset? Power on reset?

2. Will the bit F_SWT0_RES set if the reset occurs because watchdog was not refreshed? meaning no Flash Initialization failure.

There 2 separate things. If you have reset from SWT0 you will see the flag in FCCU set for SWT0. [NCF14]

If there is flash failure init (flash initialization time is guarded by SWT0 during reset phase) you will see set F_SWT0_RES

Personalty I never seen flash init failure.

3. Is there a way to trigger a functional reset when Watchdog is not refreshed?

On the first timeout you can trigger external interrup -> in ISR you can trigger software functional reset via RGM module.

On second timeout it is considered as critical fault.

regards,

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Peter,

Thank you for your response.

What I am trying to do is to trigger a reset by not refreshing the Watchdog timer.

I get the bit F_SWT0_RES set in MC_RGM_DES every time.

The confusion is now I do not know if the reset was caused by SWT0 reset or if a Flash initialization failure has occured.

I wanted know if F_SWT0_RES bit is set exclusively for Flash initialization failure.

Or does SWT0 triggers a destructive reset which causes this bit to set?

Best regards,

Sachin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

What I am trying to do is to trigger a reset by not refreshing the Watchdog timer.

I do not understand this. Reset by not refreshing the SWT? So it is reset in SWT timeout?

If yes, than just configure SWT to trigger reset on SWT expire. (in SWT and FCCU module) if not configured yet.

I get the bit F_SWT0_RES set in MC_RGM_DES every time.

If you are not refreshing the SWT, than it is correct.

The confusion is now I do not know if the reset was caused by SWT0 reset or if a Flash initialization failure has occurred.

Well if the flash init failure is the reason than SWT will trigger destructive reset after the flash init is done until the flash initialization is correctly done or reset escalation is triggered.

In order to ensure that this happens within a reasonable time, the SWT is brought out of reset for PHASE2[FUNC]/PHASE2[DEST] RESET. So, if the SWT times out during this time, the flash’s initialization sequence was not able to complete. This is also referred as SWT0 (flash initialization error).

In order to trigger another attempt at initializing the flash, a ‘destructive’ reset is generated. If it occurs repeatedly, the ‘destructive’ reset escalator in the MC_RGM will increment until it finally keeps the chip in reset until the next power-on reset. This is to prevent unnecessary power consumption due to reset cycling.

But I think there is not possible to recognize the root cause of SWT timeout.

I wanted know if F_SWT0_RES bit is set exclusively for Flash initialization failure.

Or does SWT0 triggers a destructive reset which causes this bit to set?

SWT0 trigger dest reset which set F_SWT0_RES.

regards,

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Peter,

Thank you very much!

Your explanations are very helpful.

Best regards,

Sachin