- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- MPC5746C AXBS PRS[7] and CRS[7] fail to read

MPC5746C AXBS PRS[7] and CRS[7] fail to read

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MPC5746C AXBS PRS[7] and CRS[7] fail to read

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

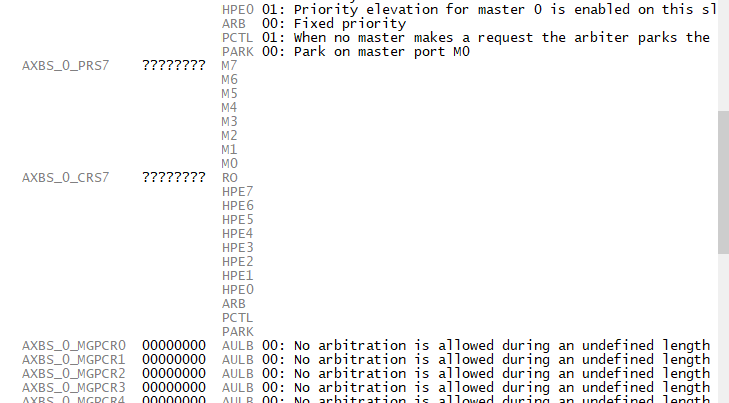

The program locks up when I try to read AXBS PRS[7] and/or AXBS CRS[7].

MGPCR[7] seems to work just fine, but the answer is always 0. (Perhaps its supposed to be 0?)

unsigned long R1 = AXBS_0.PORT[7].PRS.R <- Program locks up. No IOVR

unsigned long R2 = AXBS_0.PORT[7].CRS.R <- Program locks up. No IOVR

unsigned long R3 = AXBS_0.MGPCR[7].MGPCR.R <- Works just fine.

I know it should be working, since there are 8.

AXBS_PORT_tag PORT[8];

AXBS_MGPCR_tag MGPCR[8];

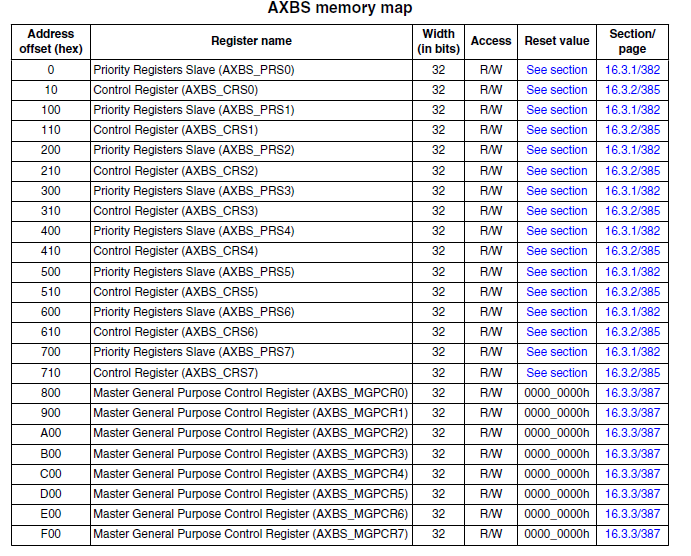

The Reference manual shows that as well.

I don't know if there is a problem with the Header file, but I have included it.

/* ============================================================================

=============================== Module: AXBS ===============================

============================================================================ */

typedef union AXBS_PORT_PRS_union_tag { /* Priority Registers Slave */

vuint32_t R;

struct {

vuint32_t _unused_31:1;

vuint32_t M7:3; /* Master 7 Priority. Sets the arbitration priority for this port on the associated slave port. */

vuint32_t _unused_27:1;

vuint32_t M6:3; /* Master 6 Priority. Sets the arbitration priority for this port on the associated slave port. */

vuint32_t _unused_23:1;

vuint32_t M5:3; /* Master 5 Priority. Sets the arbitration priority for this port on the associated slave port. */

vuint32_t _unused_19:1;

vuint32_t M4:3; /* Master 4 Priority. Sets the arbitration priority for this port on the associated slave port. */

vuint32_t _unused_15:1;

vuint32_t M3:3; /* Master 3 Priority. Sets the arbitration priority for this port on the associated slave port. */

vuint32_t _unused_11:1;

vuint32_t M2:3; /* Master 2 Priority. Sets the arbitration priority for this port on the associated slave port. */

vuint32_t _unused_7:1;

vuint32_t M1:3; /* Master 1 Priority. Sets the arbitration priority for this port on the associated slave port. */

vuint32_t _unused_3:1;

vuint32_t M0:3; /* Master 0 Priority. Sets the arbitration priority for this port on the associated slave port. */

} B;

} AXBS_PORT_PRS_tag;

typedef union AXBS_PORT_CRS_union_tag { /* Control Register */

vuint32_t R;

struct {

vuint32_t RO:1; /* Read Only */

vuint32_t _unused_30:1;

vuint32_t _unused_24:6;

vuint32_t HPE7:1;

vuint32_t HPE6:1;

vuint32_t HPE5:1;

vuint32_t HPE4:1;

vuint32_t HPE3:1;

vuint32_t HPE2:1;

vuint32_t HPE1:1;

vuint32_t HPE0:1;

vuint32_t _unused_10:6;

vuint32_t ARB:2; /* Arbitration Mode */

vuint32_t _unused_6:2;

vuint32_t PCTL:2; /* Parking Control */

vuint32_t _unused_3:1;

vuint32_t PARK:3; /* Park */

} B;

} AXBS_PORT_CRS_tag;

typedef struct AXBS_PORT_struct_tag {

AXBS_PORT_PRS_tag PRS; /* Priority Registers Slave */

uint8_t PORT_reserved0[12];

AXBS_PORT_CRS_tag CRS; /* Control Register */

uint8_t PORT_reserved1[236];

} AXBS_PORT_tag;

typedef union AXBS_MGPCR_MGPCR_union_tag { /* Master General Purpose Control Register */

vuint32_t R;

struct {

vuint32_t _unused_3:29;

vuint32_t AULB:3; /* Arbitrates On Undefined Length Bursts */

} B;

} AXBS_MGPCR_MGPCR_tag;

typedef struct AXBS_MGPCR_struct_tag {

AXBS_MGPCR_MGPCR_tag MGPCR; /* Master General Purpose Control Register */

uint8_t MGPCR_reserved0[252];

} AXBS_MGPCR_tag;

struct AXBS_tag {

AXBS_PORT_tag PORT[8];

AXBS_MGPCR_tag MGPCR[8];

};

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

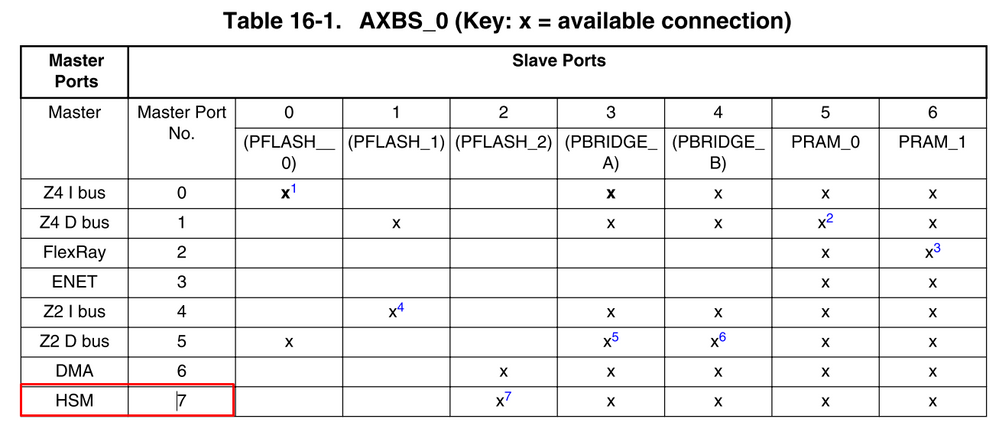

looking into latest device cut I can see that PRS7 and CRS7 are not implemented or accessible for read/write operation.

I expect that they are assigned to HSM module.

See the screen below. Reading them will result into IVOR1.

regards,

Peter