- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

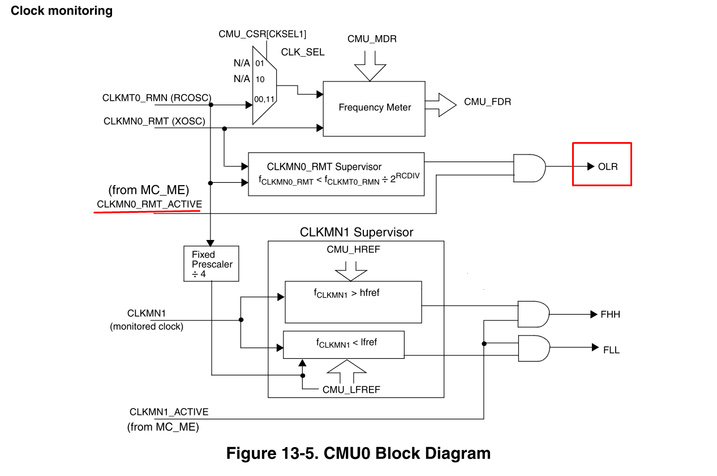

I am trying to enable the clock monitor feature in the MPC5744P controller which monitors the external clock(XOSC->40MHz) using internal clock(IROSC-16MHz) as the reference.

First of all I want to clarify few things regarding the clock monitor like:-

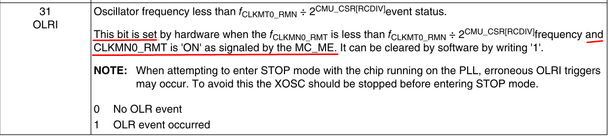

- If the Clock monitor feature is enabled by setting the CMU.CSR.RCDIV and CMU.CSR.CME, the CMU.ISR.OLRI bit should be set if XOSC<IOSC (if RCDIV is 0) right? is there any additional configuration required? whether the OLRI bit is set only if clock is not available in the beginning? what if clock is there in the beginning and later there is some issue in the XOSC clock and it is going unstable after the initialization process? Still the OLRI bit is set in this case?

- I have tried configuring the FCCU for the above fault(fccu fault id 26), but if we configure short or long reset for the above fault, does the controller reset? If yes, then how to detect it as we would have lost XOSC clock and even watchdog timer(WDT) or WDT toggle would need peripheral clock for its operation which in turn comes from XOSC?

- How to switch to internal clock(IROSC) immediately when the XOSC is lost? can u please brief the steps to switch to IROSC here(pseudocode would be much appreciated)?

- Even if the clock is switched to IROSC when XOSC is lost, how is it prescaled? because IROSC is 16MHz and XOSC is 40MHz, and how is it matched so that few peripherals would still continue to work?

- I have referred the following application note on Clock Monitor and handling the crystal failure form NXP (link here:- https://www.nxp.com/docs/en/application-note/AN4880.pdf) , and also tried the pseudocode here, but the this is not detecting the loss of XOSC and the OLRI bit is not set when I checked in the watch window.

Can you please check the above things and clarify @petervlna ? Thank you in advance

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

It makes no sense to detect if crystal is removed when it is not turned on in ME.

The device simply do not use it so it is not affecting safety of the device.

In the moment you turn it on you will know it is not working, and the clock switch will not pass, so the device will operate with its previous clock.

best regards,

Peter

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

If the Clock monitor feature is enabled by setting the CMU.CSR.RCDIV and CMU.CSR.CME, the CMU.ISR.OLRI bit should be set if XOSC<IOSC (if RCDIV is 0) right?

Yes, this is correct in case:

is there any additional configuration required?

See above

whether the OLRI bit is set only if clock is not available in the beginning?

What do you mean? Could you elaborate closer?

what if clock is there in the beginning and later there is some issue in the XOSC clock and it is going unstable after the initialization process? Still the OLRI bit is set in this case?

XOSC clock you mean? Then CMU if enabled and set will trigger OLR line. As picture above represents.

I have tried configuring the FCCU for the above fault(fccu fault id 26), but if we configure short or long reset for the above fault, does the controller reset? If yes, then how to detect it as we would have lost XOSC clock and even watchdog timer(WDT) or WDT toggle would need peripheral clock for its operation which in turn comes from XOSC?

The controller will take configured action in FCCU. FCCU and all safety related features are clock from safety clock (IRC).

How to switch to internal clock(IROSC) immediately when the XOSC is lost? can u please brief the steps to switch to IROSC here(pseudocode would be much appreciated)?

If your device is clocked from XOSC, and you loose clock, you need to take reset trough FCCU and after reset you will boot from IRC clock and analyze the fault sources.

-

Even if the clock is switched to IROSC when XOSC is lost, how is it prescaled? because IROSC is 16MHz and XOSC is 40MHz, and how is it matched so that few peripherals would still continue to work?

[Peter] - Safety peripherals are clocked from IRC. So the device will take appropriate action. Which in case of loss of clock is reset.

Best regards,

Peter

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Peter,

Thank you for the reply. Have some more clarifications as listed below:-

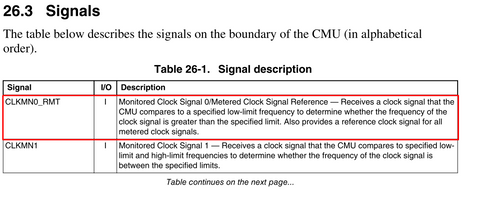

- What do you mean by "CLKMN0_RMT" is ON as signalled by MC_ME? Should we set some bit in the MC_ME register? Where does that CLKMN0_RMT_ACTIVE come from?

- "whether the OLRI bit is set only if clock is not available in the beginning?"---> I mean whether the OLRI bit is set or not when the XOSC clock is stable during the initialization process and after that the XOSC clock is going unstable and becoming less than IROSC?

- Does the clock automatically switch from XOSC to IROSC if short or long functional reset is configured in the FCCU module(fault id 26) when the OLRI bit is set? Any additional configurations are required for clock switching other than FCCU?

- Does this pseudocode in the application note https://www.nxp.com/docs/en/application-note/AN4880.pdf works with those configurations for loss of clock detection and reaction? Any additional configurations required?

Thank you in advance

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

What do you mean by "CLKMN0_RMT" is ON as signalled by MC_ME? Should we set some bit in the MC_ME register? Where does that CLKMN0_RMT_ACTIVE come from?

So the clock must be enabled in Mode entry mode in the mode where you doing measurement. (XOSC)

"whether the OLRI bit is set only if clock is not available in the beginning?"---> I mean whether the OLRI bit is set or not when the XOSC clock is stable during the initialization process and after that the XOSC clock is going unstable and becoming less than IROSC?

No, it is set when you enable CMU, as the schematic represents.

Does the clock automatically switch from XOSC to IROSC if short or long functional reset is configured in the FCCU module(fault id 26) when the OLRI bit is set? Any additional configurations are required for clock switching other than FCCU?

Yes, the default clock after reset is IRC clock. As it is considered as safety clock, so you can do safety analyzes on your SW.

Does this pseudocode in the application note https://www.nxp.com/docs/en/application-note/AN4880.pdf works with those configurations for loss of clock detection and reaction? Any additional configurations required?

I am not author of the AN, but the code looks fine to me. for any safety critical application parts I recommend to not rely on example codes, but rather on your own code.

Best regards,

Peter

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Peter,

Thank you so much for the reply and your inputs @petervlna . I was able to test the CMU by removing the XOSC crystal from the board and by providing external frequency from the signal generator which is less than the IROSC frequency and observed that OLRI bit is set and the board was getting reset.

I have one question regarding the crystal failure:

What if the crystal is removed from the board and there is no XOSC ON signal from the MC_ME reg and how to detect the crystal failure condition in this case? Is there any way to detect this using CMU/FCCU or any other feature in MPC?

Thank you in advance

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

It makes no sense to detect if crystal is removed when it is not turned on in ME.

The device simply do not use it so it is not affecting safety of the device.

In the moment you turn it on you will know it is not working, and the clock switch will not pass, so the device will operate with its previous clock.

best regards,

Peter

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Okay, got it. Thank you so much for the support @petervlna

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Please clarify the above topics asap as this feature is crucial for our project. Thank you