- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Re: MPC5644A - eDMA Trial

MPC5644A - eDMA Trial

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

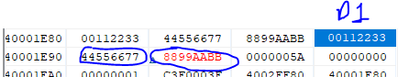

I just want to transfer data from source to destination like ;

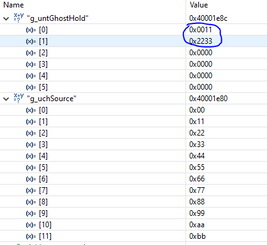

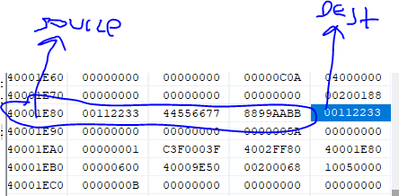

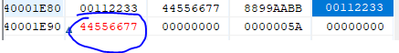

Source : uint8 g_uchSource[12] --> the address is 0x40001e80

Source variables are : 0x00 , 0x11 , 0x22 , 0x33, 0x44 , 0x55, 0x66 , 0x77, 0x88, 0x99, 0xAA , 0xBB

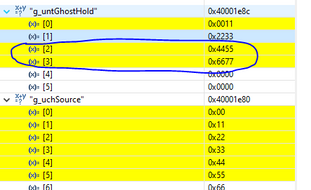

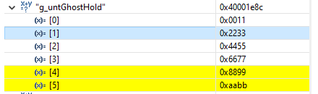

Destination : uint16 g_untGhostHold[6]. --> the address is 0x40001e8c

The DMA TCD is arranged as :

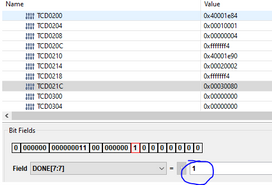

EDMA.TCD[CH2].SADDR = (vuint32)&g_uchSource;

EDMA.TCD[CH2].DADDR = (vuint32)&g_untGhostHold;

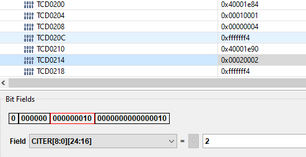

EDMA.TCD[CH2].CITER = (vuint16)3;

EDMA.TCD[CH2].BITER = (vuint16)3;

EDMA.TCD[CH2].SSIZE = 0; //8 bit source size

EDMA.TCD[CH2].DSIZE = 1; //16 bit destination size

EDMA.TCD[CH2].NBYTES = 4; //4 bytes will be transferred for each major iteration

EDMA.TCD[CH2].SLAST = (vuint32)(-1*12); //return

EDMA.TCD[CH2].CITERE_LINK = 0;

EDMA.TCD[CH2].BITERE_LINK = 0;

EDMA.TCD[CH2].BWC = 0;

EDMA.TCD[CH2].DLAST_SGA = (vuint32)(-2*6); //return

EDMA.TCD[CH2].SMOD = 0;

EDMA.TCD[CH2].DMOD = 0;

EDMA.TCD[CH2].SOFF = 1; //Source minor address iteration will be 1 byte

EDMA.TCD[CH2].DOFF = 2; //Destination 2 byte

EDMA.TCD[CH2].MAJORE_LINK = 0;

EDMA.TCD[CH2].MAJORLINKCH = 0;

EDMA.TCD[CH2].E_SG = 0;

EDMA.TCD[CH2].D_REQ = 0;

EDMA.TCD[CH2].INT_HALF = 0;

EDMA.TCD[CH2].INT_MAJ = 0;

EDMA.TCD[CH2].ACTIVE = 0;

EDMA.TCD[CH2].DONE = 0;

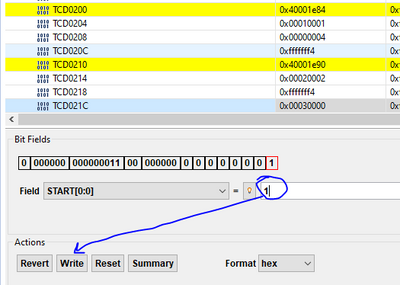

EDMA.TCD[CH2].START = 0;

Then I set the TCD.START bit in the software.

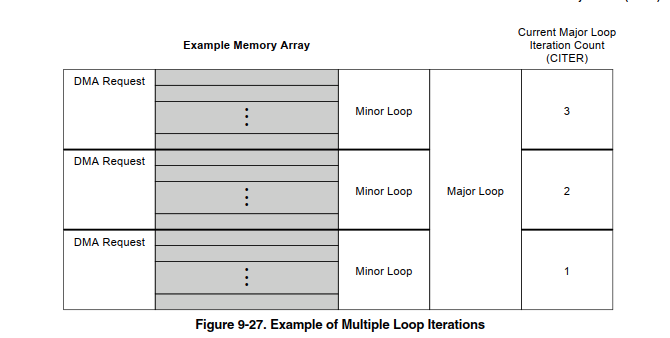

I expected that it would work like this :

1. Major (CITER = 3)

- 1.Minor -> read(0x40001e80) , read(0x40001e81)

write(0x40001e8c)

- 2.Minor -> read(0x40001e82) , read (0x40001e83)

write(0x40001e8e)

2. Major (CITER = 2)

- 1.Minor -> read(0x40001e84) , read(0x40001e85)

write(0x40001e90)

- 2. Minor -> read(0x40001e86) , read(0x40001e87)

write(0x40001e92)

3. Major (CITER = 1)

- 1. Minor -> read(0x40001e88), read(0x40001e89)

write(0x40001e94)

- 2. Minor -> read(0x40001e8A), read(0x40001e8B)

write(0x40001e96)

Then Majors are complete, TCD.DONE will be set.

However it didn't work as I expected.

In experiment :

After the first major iteration ,DMA stops. CITER decreased just once and 4 byte transfer occured as shown below.

Then I set the TCD_START bit manually.

Then other 4 byte transferred correctly. CITER decreased again.

Again, I set TCD_Start bit manually , The TCD_DONE bit is set at this time.

All transfers were done correctly by setting TCD_START bit manually for every major iteration break, but the question is that why doesn't DMA continue to work by itself after the first major iteration done until TCD_DONE occurs ?

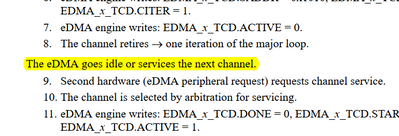

I searched referance manual (Page 589), it's given a similar example but it is hardware request.

There is a sentence like this :

Probably , eDMA goes idle in my case right ?

I do this transfer with single request just setting CITER = 1 and NBYTE = 12. It works.

I tried different channel but no change.

Do I have to do this transfer with hardware request ? But it's not any specific signal or module.

Thank you in advance.

Best regards.

SS.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, it is correct behavior. Every time CITER is decreased, new DMA request is needed. DMA request means either HW request from other module or assertion of START bit by SW.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, it is correct behavior. Every time CITER is decreased, new DMA request is needed. DMA request means either HW request from other module or assertion of START bit by SW.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I thought that those minor requests will trigger by themselves until major complete. That was the hardware request. I missed this point. Thank you so much @davidtosenovjan.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

.