- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

MPC5644A: DSPI_MCR[SMPL_PT] cannot be used with CPHA=1?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

The MPC5644A RM Rev 6 "Functional description" only talks about SMPL_PT field in the "30.9.6.3 Modified SPI/DSI transfer format (MTFE = 1, CPHA = 0)" chapter, No word about it in "30.9.6.4 Modified SPI/DSI transfer format (MTFE = 1, CPHA = 1)". However, according to its description in the MCR register, it is not tied to any particular CPHA setting.

It would be useful for us to delay by 1 or 2 system clocks the sample point of the DSPI SIN (we are in master mode, CPHA=1, CPOL=0). Can we interpreet the Data Setup Time for Inputs (tSUI) of the datasheet (Rev. 7) of 20 ns (for 5V input) as being the time between the SIN data being value and the sample point? If so, then the requirement would become 20 - 2*1/150MHz = 7 ns between data valid and clock rising edge.

Thanks,

Étienne

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Étienne,

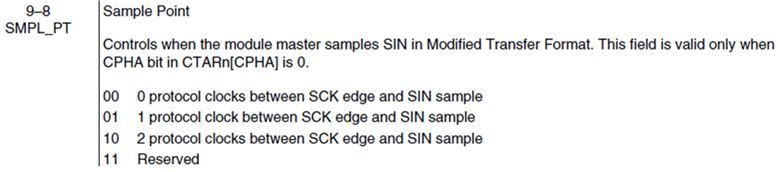

Unfortunately the relationship between SMPL_PT and CPHA is not detailed in the MPC5644A RM. However I can confirm that the SMPL_PT bit is only valid in the case where MTFE = 1 and CPHA = 0. Here's an excerpt from another device's RM for the same SPI/DSPI module:

If you wish to use the SMPL_PT delays then you will have to change your CPHA to 0.

I hope this helps!

Thanks,

David

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks. So, with MTFE=1 and CPHA=1, is this field don't care or we have to set it to 0?

Étienne