- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Is my STCU2 record correct?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

I am programming the STCU2 module of my MPC5777C mcu. I have used the DCF config generator excel file to write the necessary instructions for offline test both for l and m bists, and I do not have a lot of resources to try for more than 3 times.

I have generated the following instructions according to the reference manual:

| data.set 0x00400310 %QUAD 0xD3FEA98B00080008 ;STCU_SCK 1st write | S30D00400310D3FEA98B000800088A | ||

| data.set 0x00400318 %QUAD 0x2C01567400080008 | S30D004003182C0156740008000890 | ||

| data.set 0x00400320 %QUAD 0x0000000000080040 ;STCU_LBU_FM | S30D00400320000000000008004047 | ||

| data.set 0x00400328 %QUAD 0x0000000000080074 ;STCU_MBU_FML[31:0] | S30D0040032800000000000800740B | ||

| data.set 0x00400330 %QUAD 0x0000000000080078 ;STCU_MBU_FMM[31:0] | S30D004003300000000000080078FF | ||

| data.set 0x00400338 %QUAD 0x000000000008007C ;STCU_MBU_FMH[31:0] | S30D00400338000000000008007CF3 | ||

| data.set 0x00400340 %QUAD 0x0000000000080028 ;STCU_ERR_FM | S30D0040034000000000000800283F | ||

| data.set 0x00400348 %QUAD 0x0103450400080100 ;STCU_LB_CTRL_0 | S30D00400348010345040008010012 | ||

| data.set 0x00400350 %QUAD 0x000004C000080104 ;STCU_LB_PCS_0 | S30D00400350000004C0000801048F | ||

| data.set 0x00400358 %QUAD 0x638CABD300080110 ;STCU_LB_MISREL_0 | S30D00400358638CABD300080110D2 | ||

| data.set 0x00400360 %QUAD 0xF6FEF13400080114 ;STCU_LB_MISREH_0 | S30D00400360F6FEF134000801141A | ||

| data.set 0x00400368 %QUAD 0x0203450400080140 ;STCU_LB_CTRL_1 | S30D004003680203450400080140B1 | ||

| data.set 0x00400370 %QUAD 0x0000034000080144 ;STCU_LB_PCS_1 | S30D004003700000034000080144B0 | ||

| data.set 0x00400378 %QUAD 0x29CAE1DA00080150 ;STCU_LB_MISREL_1 | S30D0040037829CAE1DA0008015031 | ||

| data.set 0x00400380 %QUAD 0xF547396A00080154 ;STCU_LB_MISREH_1 | S30D00400380F547396A00080154F4 | ||

| data.set 0x00400388 %QUAD 0x2C01567400080008 ;STCU_SCK service WDG | S30D004003882C0156740008000820 | ||

| data.set 0x00400390 %QUAD 0x0303450400080180 ;STCU_LB_CTRL_2 | S30D00400390030345040008018048 | ||

| data.set 0x00400398 %QUAD 0x0000050000080184 ;STCU_LB_PCS_2 | S30D00400398000005000008018486 | ||

| data.set 0x004003A0 %QUAD 0x1AC8F17C00080190 ;STCU_LB_MISREL_2 | S30D004003A01AC8F17C0008019028 | ||

| data.set 0x004003A8 %QUAD 0x84F6497900080194 ;STCU_LB_MISREH_2 | S30D004003A884F64979000801942F | ||

| data.set 0x004003B0 %QUAD 0x04034504000801C0 ;STCU_LB_CTRL_3 | S30D004003B004034504000801C0E7 | ||

| data.set 0x004003B8 %QUAD 0x00000780000801C4 ;STCU_LB_PCS_3 | S30D004003B800000780000801C4A4 | ||

| data.set 0x004003C0 %QUAD 0x2A96C340000801D0 ;STCU_LB_MISREL_3 | S30D004003C02A96C340000801D054 | ||

| data.set 0x004003C8 %QUAD 0x84756583000801D4 ;STCU_LB_MISREH_3 | S30D004003C884756583000801D42A | ||

| data.set 0x004003D0 %QUAD 0x0503450400080200 ;STCU_LB_CTRL_4 | S30D004003D0050345040008020086 | ||

| data.set 0x004003D8 %QUAD 0x00000A4000080204 ;STCU_LB_PCS_4 | S30D004003D800000A400008020481 | ||

| data.set 0x004003E0 %QUAD 0x15C9A73F00080210 ;STCU_LB_MISREL_4 | S30D004003E015C9A73F00080210F3 | ||

| data.set 0x004003E8 %QUAD 0xBD55BE6A00080214 ;STCU_LB_MISREH_4 | S30D004003E8BD55BE6A0008021471 | ||

| data.set 0x004003F0 %QUAD 0x7F03450400080240 ;STCU_LB_CTRL_5 | S30D004003F07F03450400080240AC | ||

| data.set 0x004003F8 %QUAD 0x0000177600080244 ;STCU_LB_PCS_5 | S30D004003F80000177600080244DE | ||

| data.set 0x00400400 %QUAD 0x9B9F264C00080250 ;STCU_LB_MISREL_5 | S30D004004009B9F264C00080250AA | ||

| data.set 0x00400408 %QUAD 0x2C01567400080008 ;STCU_SCK service WDG | S30D004004082C015674000800089F | ||

| data.set 0x00400410 %QUAD 0xE85AA33F00080254 ;STCU_LB_MISREH_5 | S30D00400410E85AA33F000802541E | ||

| data.set 0x00400418 %QUAD 0x1100000000080600 ;STCU_MB_CTRL_0 | S30D0040041811000000000806007D | ||

| data.set 0x00400420 %QUAD 0x1200000000080604 ;STCU_MB_CTRL_1 | S30D00400420120000000008060470 | ||

| data.set 0x00400428 %QUAD 0x1300000000080608 ;STCU_MB_CTRL_2 | S30D00400428130000000008060863 | ||

| data.set 0x00400430 %QUAD 0x140000000008060C ;STCU_MB_CTRL_3 | S30D00400430140000000008060C56 | ||

| data.set 0x00400438 %QUAD 0x1500000000080610 ;STCU_MB_CTRL_4 | S30D00400438150000000008061049 | ||

| data.set 0x00400440 %QUAD 0x1600000000080614 ;STCU_MB_CTRL_5 | S30D0040044016000000000806143C | ||

| data.set 0x00400448 %QUAD 0x1700000000080618 ;STCU_MB_CTRL_6 | S30D0040044817000000000806182F | ||

| data.set 0x00400450 %QUAD 0x180000000008061C ;STCU_MB_CTRL_7 | S30D00400450180000000008061C22 | ||

| data.set 0x00400458 %QUAD 0x1900000000080620 ;STCU_MB_CTRL_8 | S30D00400458190000000008062015 | ||

| data.set 0x00400460 %QUAD 0x1A00000000080624 ;STCU_MB_CTRL_9 | S30D004004601A0000000008062408 | ||

| data.set 0x00400468 %QUAD 0x1B00000000080628 ;STCU_MB_CTRL_10 | S30D004004681B00000000080628FB | ||

| data.set 0x00400470 %QUAD 0x1C0000000008062C ;STCU_MB_CTRL_11 | S30D004004701C0000000008062CEE | ||

| data.set 0x00400478 %QUAD 0x1D00000000080630 ;STCU_MB_CTRL_12 | S30D004004781D00000000080630E1 | ||

| data.set 0x00400480 %QUAD 0x2C01567400080008 ;STCU_SCK service WDG | S30D004004802C0156740008000827 | ||

| data.set 0x00400488 %QUAD 0x1E00000000080634 ;STCU_MB_CTRL_13 | S30D004004881E00000000080634CC | ||

| data.set 0x00400490 %QUAD 0x1F00000000080638 ;STCU_MB_CTRL_14 | S30D004004901F00000000080638BF | ||

| data.set 0x00400498 %QUAD 0x200000000008063C ;STCU_MB_CTRL_15 | S30D00400498200000000008063CB2 | ||

| data.set 0x004004A0 %QUAD 0x2100000000080640 ;STCU_MB_CTRL_16 | S30D004004A02100000000080640A5 | ||

| data.set 0x004004A8 %QUAD 0x2200000000080644 ;STCU_MB_CTRL_17 | S30D004004A8220000000008064498 | ||

| data.set 0x004004B0 %QUAD 0x2300000000080648 ;STCU_MB_CTRL_18 | S30D004004B023000000000806488B | ||

| data.set 0x004004B8 %QUAD 0x240000000008064C ;STCU_MB_CTRL_19 | S30D004004B8240000000008064C7E | ||

| data.set 0x004004C0 %QUAD 0x2500000000080650 ;STCU_MB_CTRL_20 | S30D004004C0250000000008065071 | ||

| data.set 0x004004C8 %QUAD 0x2600000000080654 ;STCU_MB_CTRL_21 | S30D004004C8260000000008065464 | ||

| data.set 0x004004D0 %QUAD 0x2700000000080658 ;STCU_MB_CTRL_22 | S30D004004D0270000000008065857 | ||

| data.set 0x004004D8 %QUAD 0x280000000008065C ;STCU_MB_CTRL_23 | S30D004004D8280000000008065C4A | ||

| data.set 0x004004E0 %QUAD 0x2900000000080660 ;STCU_MB_CTRL_24 | S30D004004E029000000000806603D | ||

| data.set 0x004004E8 %QUAD 0x2A00000000080664 ;STCU_MB_CTRL_25 | S30D004004E82A0000000008066430 | ||

| data.set 0x004004F0 %QUAD 0x2B00000000080668 ;STCU_MB_CTRL_26 | S30D004004F02B0000000008066823 | ||

| data.set 0x004004F8 %QUAD 0x2C0000000008066C ;STCU_MB_CTRL_27 | S30D004004F82C0000000008066C16 | ||

| data.set 0x00400500 %QUAD 0x2D00000000080670 ;STCU_MB_CTRL_28 | S30D004005002D0000000008067008 | ||

| data.set 0x00400508 %QUAD 0x2E00000000080674 ;STCU_MB_CTRL_29 | S30D004005082E00000000080674FB | ||

| data.set 0x00400510 %QUAD 0x2C01567400080008 ;STCU_SCK service WDG | S30D004005102C0156740008000896 | ||

| data.set 0x00400518 %QUAD 0x2F00000000080678 ;STCU_MB_CTRL_30 | S30D004005182F00000000080678E6 | ||

| data.set 0x00400520 %QUAD 0x300000000008067C ;STCU_MB_CTRL_31 | S30D00400520300000000008067CD9 | ||

| data.set 0x00400528 %QUAD 0x3100000000080680 ;STCU_MB_CTRL_32 | S30D004005283100000000080680CC | ||

| data.set 0x00400530 %QUAD 0x3200000000080684 ;STCU_MB_CTRL_33 | S30D004005303200000000080684BF | ||

| data.set 0x00400538 %QUAD 0x3300000000080688 ;STCU_MB_CTRL_34 | S30D004005383300000000080688B2 | ||

| data.set 0x00400540 %QUAD 0x340000000008068C ;STCU_MB_CTRL_35 | S30D00400540340000000008068CA5 | ||

| data.set 0x00400548 %QUAD 0x3500000000080690 ;STCU_MB_CTRL_36 | S30D00400548350000000008069098 | ||

| data.set 0x00400550 %QUAD 0x3600000000080694 ;STCU_MB_CTRL_37 | S30D0040055036000000000806948B | ||

| data.set 0x00400558 %QUAD 0x3700000000080698 ;STCU_MB_CTRL_38 | S30D0040055837000000000806987E | ||

| data.set 0x00400560 %QUAD 0x380000000008069C ;STCU_MB_CTRL_39 | S30D00400560380000000008069C71 | ||

| data.set 0x00400568 %QUAD 0x39000000000806A0 ;STCU_MB_CTRL_40 | S30D0040056839000000000806A064 | ||

| data.set 0x00400570 %QUAD 0x3A000000000806A4 ;STCU_MB_CTRL_41 | S30D004005703A000000000806A457 | ||

| data.set 0x00400578 %QUAD 0x3B000000000806A8 ;STCU_MB_CTRL_42 | S30D004005783B000000000806A84A | ||

| data.set 0x00400580 %QUAD 0x3C000000000806AC ;STCU_MB_CTRL_43 | S30D004005803C000000000806AC3D | ||

| data.set 0x00400588 %QUAD 0x3D000000000806B0 ;STCU_MB_CTRL_44 | S30D004005883D000000000806B030 | ||

| data.set 0x00400590 %QUAD 0x3E000000000806B4 ;STCU_MB_CTRL_45 | S30D004005903E000000000806B423 | ||

| data.set 0x00400598 %QUAD 0x3F000000000806B8 ;STCU_MB_CTRL_46 | S30D004005983F000000000806B816 | ||

| data.set 0x004005A0 %QUAD 0x2C01567400080008 ;STCU_SCK service WDG | S30D004005A02C0156740008000806 | ||

| data.set 0x004005A8 %QUAD 0x40000000000806BC ;STCU_MB_CTRL_47 | S30D004005A840000000000806BC01 | ||

| data.set 0x004005B0 %QUAD 0x41000000000806C0 ;STCU_MB_CTRL_48 | S30D004005B041000000000806C0F4 | ||

| data.set 0x004005B8 %QUAD 0x42000000000806C4 ;STCU_MB_CTRL_49 | S30D004005B842000000000806C4E7 | ||

| data.set 0x004005C0 %QUAD 0x43000000000806C8 ;STCU_MB_CTRL_50 | S30D004005C043000000000806C8DA | ||

| data.set 0x004005C8 %QUAD 0x44000000000806CC ;STCU_MB_CTRL_51 | S30D004005C844000000000806CCCD | ||

| data.set 0x004005D0 %QUAD 0x45000000000806D0 ;STCU_MB_CTRL_52 | S30D004005D045000000000806D0C0 | ||

| data.set 0x004005D8 %QUAD 0x46000000000806D4 ;STCU_MB_CTRL_53 | S30D004005D846000000000806D4B3 | ||

| data.set 0x004005E0 %QUAD 0x47000000000806D8 ;STCU_MB_CTRL_54 | S30D004005E047000000000806D8A6 | ||

| data.set 0x004005E8 %QUAD 0x48000000000806DC ;STCU_MB_CTRL_55 | S30D004005E848000000000806DC99 | ||

| data.set 0x004005F0 %QUAD 0x49000000000806E0 ;STCU_MB_CTRL_56 | S30D004005F049000000000806E08C | ||

| data.set 0x004005F8 %QUAD 0x4A000000000806E4 ;STCU_MB_CTRL_57 | S30D004005F84A000000000806E47F | ||

| data.set 0x00400600 %QUAD 0x4B000000000806E8 ;STCU_MB_CTRL_58 | S30D004006004B000000000806E871 | ||

| data.set 0x00400608 %QUAD 0x4C000000000806EC ;STCU_MB_CTRL_59 | S30D004006084C000000000806EC64 | ||

| data.set 0x00400610 %QUAD 0x4D000000000806F0 ;STCU_MB_CTRL_60 | S30D004006104D000000000806F057 | ||

| data.set 0x00400618 %QUAD 0x4E000000000806F4 ;STCU_MB_CTRL_61 | S30D004006184E000000000806F44A | ||

| data.set 0x00400620 %QUAD 0x4F000000000806F8 ;STCU_MB_CTRL_62 | S30D004006204F000000000806F83D | ||

| data.set 0x00400628 %QUAD 0x50000000000806FC ;STCU_MB_CTRL_63 | S30D0040062850000000000806FC30 | ||

| data.set 0x00400630 %QUAD 0x0000000000080700 ;STCU_MB_CTRL_64 | S30D00400630000000000008070074 | ||

| data.set 0x00400638 %QUAD 0xFFFFFFFF00080014 ;STCU_WDG | S30D00400638FFFFFFFF000800145C | ||

| data.set 0x00400640 %QUAD 0x1000000D0008000C ;STCU_CFG | S30D004006401000000D0008000C3B | ||

| data.set 0x00400648 %QUAD 0x0205003200080010 ;STCU_PLL_CFG | S30D00400648020500320008001013 | ||

| data.set 0x00400650 %QUAD 0x0000030100080000 ;STCU_RUN | S30D00400650000003010008000050 |

I must add that this excel file generates wrong checksum values for some srec records, and I use them via a script I have wrote by using Python.

Could you verify if my instructions are correct or not? If I embed the corrected srec to the mcu, is it going to work? Can I show if STCU2 module is working correctly via a manual or a paper? Because as far as I understand, there is no way to corrupt the device without actually harming it.

Thanks in advance.

Best wishes

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

Well, programming the STCU based on your own configuration.. I would not recommend doing that unless you have deep knowledge on STCU mechanism and lot of testing possibility.

Could you verify if my instructions are correct or not?

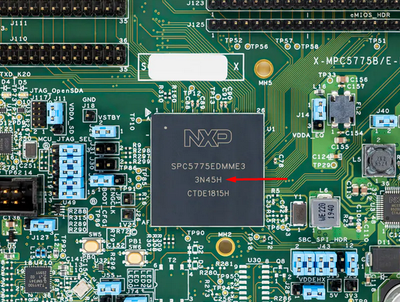

I have attached reference script. Furthermore checksums depends on device cut, which you do not share with me. So make sure you have the same as I. -> 3N45H

If I embed the corrected srec to the mcu, is it going to work?

Cant say. But if it is correct STCU configuration validated by NXP, it will.

Can I show if STCU2 module is working correctly via a manual or a paper?

Sorry, I do not understand this questions. STCU is HW module operating dependent on voltages, memory conditions, peripheries, etc...

Because as far as I understand, there is no way to corrupt the device without actually harming it.

By programming STCU DCF records, you cant harm device. But messing with UTEST flash, you definitely can corrupt device.

I suggest you to read AN:

https://community.nxp.com/t5/MPC5xxx-Knowledge-Base/MPC57xx-DCF-records/ta-p/1114884

https://www.nxp.com/docs/en/application-note/AN5288.pdf

Best regards,

Peter

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

@petervlna Thank you for explaining.

Sorry, I do not understand this questions. STCU is HW module operating dependent on voltages, memory conditions, peripheries, etc...

I must validate my configuration work somehow for certification. So ı need some result of testing by you.

how can I run the cmm file? Im using PE micro FX debugger is that important for implementing that script?

I have attached reference script. Furthermore checksums depends on device cut, which you do not share with me. So make sure you have the same as I. -> 3N45H

I meant the checksums the excel calculates.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

I must validate my configuration work somehow for certification. So ı need some result of testing by you.

Dont know which kind of certification standard you are talking about. This device is ASIL-D ready.

Anyway, we are not able to share any resources regarding testing process here on public community.

For such communication you will need NDA and rise a ticket at NXP.com

how can I run the cmm file? Im using PE micro FX debugger is that important for implementing that script?

You will need Lauterbach debugger in order to use cmm file.

I have shared it as an example of configuration. You can port the DCFs for your PE which use S3 records format.

I meant the checksums the excel calculates.

Excel should be fine. But I was talking about BIST MISR checksums. Those are MISR trough registers and they differ based on silicon cut. So make sure you have same device cut.

Otherwise when the BIST finish logic tests, it will fail as the expected and calculated MISR will not match.

Unfortunate I do not have PE script for BIST programming. Not even sure if PE allows scripting.

Best regards,

Peter

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hey @petervlna and @Furkan_26,

I also had a similar problem about the excel.

So make sure you have same device cut.

How to check this? What is a device cut?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

You can read MIDR register.

Or simply have a look at device package:

Best regards,

Peter