- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- How to put MPC777C core in Halt or Reset

How to put MPC777C core in Halt or Reset

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to put MPC777C core in Halt or Reset

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Do we have any sample code which will put either of the MPC5777C cores into HALT or RESET?

My customer is trying to hold core 1 of the MPC5777C in reset but cannot get it to work.

From the reference manual, they should be able to do so.

According to the reference manual (8.2.41 Core1 Reset Vector Register), this should be possible.

8.2.41 Core1 Reset Vector Register (SIU_RSTVEC1)

This register contains the reset vector, reset control and instruction execution type selection for Core1. The RST bit is qualified by the CORE1 halt bit in the SIU_HLT1 register, such that both must be 1 for a core reset to occur. The order in which the RST and core halt bits are asserted does not matter. After both halt and RST bits are asserted, internal logic places a request to halt the corresponding core clocks, but the core may continue to run until such time that it terminates any pending crossbar master bus cycles and interrupt controller interaction that might prevent their use by other bus masters. When all pending transactions finish, the core will be in reset state with clock stopped. Exit of reset state is done by negating either SIU_HLT1[CORE1] or the RST bit. Negating just one is enough to remove the core from reset state. Chapter 8 System Integration Unit (SIU, SIU_B) MPC5777C Reference Manual, Rev. 8, 11/2016 NXP Semiconductors 325 The reset value of the halt and RST bits for Core0 is 0 by default to allow Core0 to execute out of reset. The halt and RST bits for Core1 are 1 by default to prevent Core1 from executing out of reset. Any attempt to reset both cores by setting both RST bits will result in an immediate system reset, with the cause of the reset recorded in the SIU_RSR[CPURS] bit. NOTE The halt acknowledge bit in the SIU_HLTACK1 register will not be asserted for a core in reset state. Even though setting the halt bit is part of the procedure to put a core in reset state, the halt acknowledge bit is only asserted when the WAIT instruction is executed and the core is stopped, but not in reset state

If holding the device in reset is not possible, they could halt the core as well. But they can't get this working either.

Any help would be appreciated.

Thanks,

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Peter,

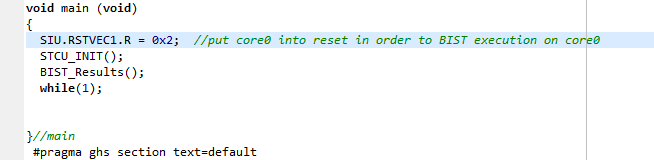

Sure we have an example. It is very simple:

This is the code for putting core0 into reset executed from core1.

you will use same for core1 while code running from core0 via RSTVEC0 register.

regards,

Peter

PS: maybe your customer trying to put in reset core0 while code is executed from core0 :smileyhappy: