- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Re: How to Enable I-CACHE & D-CACHE on MPC5674F

How to Enable I-CACHE & D-CACHE on MPC5674F

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

i try to eable i-cache and d-cache on MPC5674F,

How to find out that cache is enabled?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, please pay attention to following example code:

Example XPC567XFKIT PinToggleStationery CW210

If you open Optimizations.c file, you may see initialization of both caches.

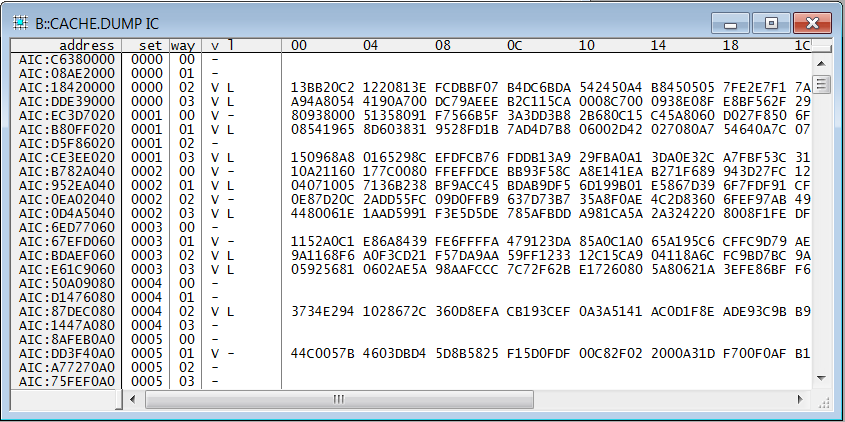

Easiest way how to check it is enabled, is to see cache content (if your debugger allows it) if there is some content there:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, please pay attention to following example code:

Example XPC567XFKIT PinToggleStationery CW210

If you open Optimizations.c file, you may see initialization of both caches.

Easiest way how to check it is enabled, is to see cache content (if your debugger allows it) if there is some content there:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, I implemented the SRAM optimizations code as you told me, and the SRAM seems to be optimized.

And I'm measuring an access time of an external SSRAM using an internal PIT module on MPC5674F.

However, the measured access time of the external SSRAM differs depending on internal SRAM settings.

(The internal SRAM access time is the same.)

I used two versions of the code to measure time.

1. a code generated by using RAppID. (This code initializes the SRAM using the assembler.)

2. a code based on the example code you attached.

I think the SRAM initialization and optimization of both codes is the same, but in the first code, the following code for stack initialization has been added.

===================================================================

stack_inSRAM:

e_lis r1, __SP_INIT@h ; Initialize stack pointer r1 to

e_or2i r1, __SP_INIT@l ; value in linker command file.

.

.

.

e_stwu r1,-64(r1) ; terminate stack

===================================================================

I do not understand why the presence of this code affects the external RAM access time. (If I add the above part to the

code 2, exception handling interrupts occur continuously.)

Will the external SRAM access time be different because of the code attached above?

How to solve this problem?