- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- FlexCAN message buffer

FlexCAN message buffer

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FlexCAN message buffer

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I have one question for FlexCan Mailbox.as mentioned in user mannual,each CAN channel support 96 message buffers.

which can be configued as rx or tx.but if the message number is greater than 96,how can we deal with the messages?

thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

did you meant what to do if you have more message to be sent/received than it is number of available message buffers? If yes then it depends on actual needs.

For transmitting messages; with the single CAN module you can use less MBs and create some SW TX queue to manage message to be sent. The MB is selected for transmission based on internal arbitration and after successful transmission the MB can be again prepared for another transmission.

For receiving messages; you can use mask acceptance registers to create ID ranges to be received, if it is possible in application. Also the RXFIFO can used where the ID table can be defined and so incoming messages is stored into RXFIFO. These ways you can reduce number of MBs needed.

Also several CAN modules can be connected to the same transceiver. This allows more RX buffers to be available for a node. But in this case, only one module is used for transmit and the other CAN module’s transmit pins are not connected. Just RX pins are connected. The receiving module should be set in Listen-only mode (CTRL1[LOM] bit set). Transmission is disabled, all error counters are frozen and the module operates in a CAN Error Passive mode. Only messages acknowledged by another CAN station will be received. If FlexCAN detects a message that has not been acknowledged, it will flag a BIT0 error, as if it was trying to acknowledge the message. RX interrupt are functional in LOM mode normally.

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi Petr

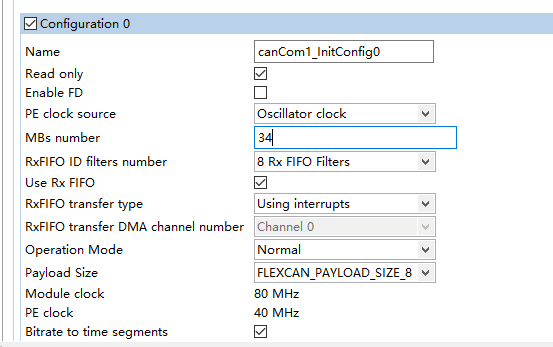

yes, I try to test the FIFO for flexCan,the main scripts are as belows:

FLEXCAN_DRV_Init(INST_CANCOM1, &canCom1_State, &canCom1_InitConfig0);

FLEXCAN_DRV_SetRxMaskType(INST_CANCOM1, FLEXCAN_RX_MASK_GLOBAL);

FLEXCAN_DRV_SetRxFifoGlobalMask(INST_CANCOM1,FLEXCAN_MSG_ID_STD,0x1FFFFFFF);

FLEXCAN_DRV_ConfigRxFifo(INST_CANCOM1,FLEXCAN_RX_FIFO_ID_FORMAT_A,&can_fifo_config);

while(1)

{

FLEXCAN_DRV_RxFifo(INST_CANCOM1,&recvBuff);

}

but unfortunately, I can't receive CAN messages in recvBuff.is there anything wrong?Do you have any suggestion?

hope your answer,thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi Petr

I download the example,and check the code.I see the filter for FIFO is working.

but I have some questions:

1,there are two kinds of MASK,one is FLEXCAN_RX_MASK_INDIVIDUAL, the other one is FLEXCAN_RX_MASK_GLOBAL.what's the difference for these two mask(s)?

2,regarding the function FLEXCAN_DRV_SetRxIndividualMask(INST_CANCOM1, FLEXCAN_MSG_ID_STD, id_counter, 0xFFFFFFFF),is the id_counter message buffer ID or the application message ID?

3,if I want to banding one message buffer with several specific application messages,how did I configure it?

4,if I use fifo and message buffer multiplexing together as shown in example,if the fifo occupied message buffer 0-7,if I try to set rx individual mask,is the message buffer starting from message buffer 8?

thank you.

Best regards

yu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

1) this configure MCR[IRMQ] bit, this bit indicates whether Rx matching process will be based either on individual masking (RXIMRn) or on masking scheme with RXMGMASK, RX14MASK and RX15MASK, RXFGMASK.

2) it is RXIMR register number

3) The Accepance mask registers are used to filter incoming ID. ID ranges can be used if mask register is set desirably. There is bit2bit correspondence between received ID, mask and programmed MB ID (or RXFIFO ID filter elements). The mask says if corresponding incoming ID bit is compared with programmed ID bit.

If mask bit is cleared the incoming ID bit is not compared, it is don’t care. If mask bit is set, then there must be exact match between incoming ID bit and programmed ID bit. To receive a message into a MB/RXFIFO all relevant bits with mask bit set must be equal to programmed one.

4) yes, in this case available MBs start from MB8

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi

thank you. One more question,if I use FLEXCAN_DRV_SetRxIndividualMask to configue each message buffer when fifo is not enabled,the mask is working.

as shown in FLEXCAN_DRV_SetRxIndividualMask,when fifo is enabled and message buffer index is greater than fifo element threshold,it will quit from freeze mode,and I can't set individul mask for some specific Mb.

In fact, I have the requirement to use both fifo and message Id MASK,in this case,how to deal with it?

here is the function for setting individual mask:

status_t FLEXCAN_DRV_SetRxIndividualMask(

uint8_t instance,

flexcan_msgbuff_id_type_t id_type,

uint8_t mb_idx,

uint32_t mask)

{

DEV_ASSERT(instance < CAN_INSTANCE_COUNT);

CAN_Type * base = g_flexcanBase[instance];

flexcan_rx_fifo_id_element_format_t formatType;

FLEXCAN_EnterFreezeMode(base);

if ((mb_idx > FLEXCAN_GetMaxMsgBuffNum(base)) || (mb_idx >= CAN_RXIMR_COUNT))

{

FLEXCAN_ExitFreezeMode(base);

return STATUS_CAN_BUFF_OUT_OF_RANGE;

}

if (false == FLEXCAN_IsRxFifoEnabled(base))

{

if (id_type == FLEXCAN_MSG_ID_STD)

{

/* Set standard individual mask*/

FLEXCAN_SetRxIndividualStdMask(base, mb_idx, mask);

}

else if (id_type == FLEXCAN_MSG_ID_EXT)

{

/* Set extended individual mask*/

FLEXCAN_SetRxIndividualExtMask(base, mb_idx, mask);

}

else

{

/* Should not get here */

}

}

else

{

if (mb_idx > FLEXCAN_GetNoOfIndividualMBsRxFIFO(base))

{

FLEXCAN_ExitFreezeMode(base);

return STATUS_CAN_BUFF_OUT_OF_RANGE;

}

/* In FIFO Mode get the Id Filter Format already configured by FLEXCAN_DRV_ConfigRxFifo */

formatType = FLEXCAN_GetRxFifoIdFormat(base);

FLEXCAN_SetRxIndividualMask(base, mb_idx,

FLEXCAN_GetRxFifoMask(id_type, formatType, mask));

}

FLEXCAN_ExitFreezeMode(base);

return STATUS_SUCCESS;

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I see no issue in the latest SDK 3.0.2

if (mb_idx <= FLEXCAN_GetNoOfIndividualMBsRxFIFO(base))

/* In FIFO Mode get the Id Filter Format already configured by FLEXCAN_DRV_ConfigRxFifo */

flexcan_rx_fifo_id_element_format_t formatType = FLEXCAN_GetRxFifoIdFormat(base);

uint32_t calcMask = FLEXCAN_GetRxFifoMask(id_type, formatType, mask); switch (formatType)

{

case FLEXCAN_RX_FIFO_ID_FORMAT_A :

FLEXCAN_SetRxIndividualMask(base, mb_idx, calcMask);

break;

case FLEXCAN_RX_FIFO_ID_FORMAT_B :

FLEXCAN_SetRxIndividualMask(base, mb_idx, (calcMask | (calcMask >> FLEXCAN_RX_FIFO_ID_FILTER_FORMATB_EXT_SHIFT1)));

break;

case FLEXCAN_RX_FIFO_ID_FORMAT_C :

FLEXCAN_SetRxIndividualMask(base, mb_idx, (calcMask | (calcMask >> FLEXCAN_RX_FIFO_ID_FILTER_FORMATC_SHIFT1) |

(calcMask >> FLEXCAN_RX_FIFO_ID_FILTER_FORMATC_SHIFT2) |

(calcMask >> FLEXCAN_RX_FIFO_ID_FILTER_FORMATC_SHIFT3)));

break;

default :

/* Will Enable all filter fields mask */

FLEXCAN_SetRxIndividualMask(base, mb_idx, 0xFFFFFFFFU);

break;

}

}

else

{

if (id_type == FLEXCAN_MSG_ID_STD)

{

/* Set standard individual mask*/

FLEXCAN_SetRxIndividualStdMask(base, mb_idx, mask);

}

else if (id_type == FLEXCAN_MSG_ID_EXT)

{

/* Set extended individual mask*/

FLEXCAN_SetRxIndividualExtMask(base, mb_idx, mask);

}

else

{

/* Should not get here */

}

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi Petr

Using FIFO+DMA, since the FIFO depth is 6, in SDK,is there any funcion which can read out the buffer message at the same time?

in SDK,I use this function FLEXCAN_DRV_RxFifo(INST_CANCOM7,&recvBuff6),it could only read out one message each time.

thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

yes, and you should use this function repeatedly to read all messages from RXFIFO.

BR, Petr