- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- EQADC RFIFO PROBLEM on MPC5777C

EQADC RFIFO PROBLEM on MPC5777C

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

EQADC RFIFO PROBLEM on MPC5777C

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello everyone;

I have a trouble about receiving data from RFIFO(0).

Firstly, I have one ADC input and so I have arranged just one channel on ADC. I am using streaming mode and I am triggerring my conversion command by PIT on each 500 ms.

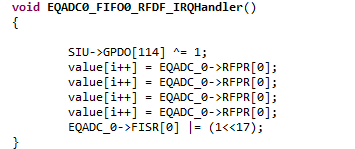

I have set relevant bits to receive interrupt when at least one data is in RFIFO(0) and I retrieve data from RFIFO to my buffer on each relevant interrupt showing RFIFO has valid entry.

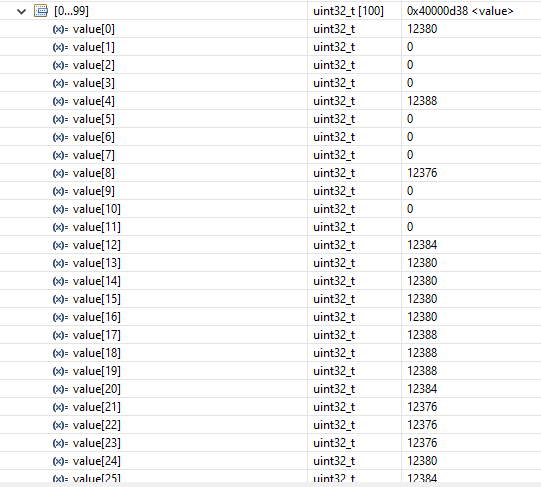

My problem is that after third interrupt, My RFIFO is full and I receive four different datas. I supposed that datas I have read do not leave RFIFO.

There is two photos below. One of them is about my buffer and another is RFIFO drain interrupt ISR function where I read data.

What can be reason for that?

I am looking forward to hearing your responds.

Sincerely.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, you should read just one result in the ISR and clear FISR[RFDF] flag in the ISR.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

When I was in debug mode, I examined each register and RFIFO(0). From my point of view, data in RFIFO(0) does not disappear even if we read it.

However, according to reference manuel, data in RFIFO(s) disappear after reading it.

Could you explain this point for me also?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Another option is that if I read RFIFO continuously, I see the last value in the RFIFO relevant index.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

When the EQADC RFIFO Pop Register x is read and RFIFOx is empty, EQADC will not

decrement the counter value and the POP Next Data Pointer x will not be updated. The

read value will be undefined.

I think, answer is above. I have copied it from reference manuel.