- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Does EIM inject an error directly into the RAM?

Does EIM inject an error directly into the RAM?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Does EIM inject an error directly into the RAM?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I was reading EIM in MPC5777C Reference manual and as per figure 17-1 it was my understanding that EIM acts between RAM and the module and if enabled simply inverts the bit and sends it to the module rather than changing the bit in the RAM memory. therefore if EIM was disabled it would send the data as it is was without inverting.

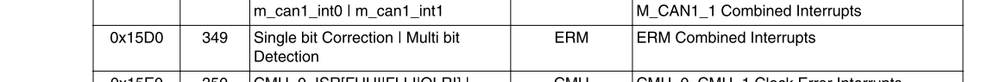

But then i saw the following example MPC5777C-1b+2b_RAM_ECC_error_injection GHS614 and i have a few questions from it

Q1 In the Function ERM_combined_isr() we first disable EIM and then get the source of error and fix it, Wont disabling the EIM module automatically fix the error caused by EIM error injection?

Q2. When we do read operation test_read = test[0]; it invokes the IVOR1 exception and goes to machine check handler which then invokes Fix_1bit_error_RAM_data() where read and write back is happening. My question is shouldn't the instruction test_temporary[0] = test[0]; in Fix_1bit_error_RAM_data() again raise an IVOR1 exception? Assuming EIM was not used to inject an error and there was an actual 1 bit error in test[].

Q3. in Fix_2bit_error_RAM_data() are we just overwriting the corrupted data with a random data ? is there something else that's happening since 2 bit error cant be fixed.

Q4. Do i need to keep the interrupts enabled in ERM as the errors generated by EIM is already handled by IVOR1 do we need the interrupt from IVOR4? was this done for some reason?

link to example https://community.nxp.com/docs/DOC-328097

Thankyou,

Regards

Michael Jihan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Q1 In the Function ERM_combined_isr() we first disable EIM and then get the source of error and fix it, Wont disabling the EIM module automatically fix the error caused by EIM error injection?

No, disabling it will cause next read to be without bit flip. Latched error will stay reported.

Q2. When we do read operation test_read = test[0]; it invokes the IVOR1 exception and goes to machine check handler which then invokes Fix_1bit_error_RAM_data() where read and write back is happening. My question is shouldn't the instruction test_temporary[0] = test[0]; in Fix_1bit_error_RAM_data() again raise an IVOR1 exception? Assuming EIM was not used to inject an error and there was an actual 1 bit error in test[].

Are you talking about single or multibit injection?

Q3. in Fix_2bit_error_RAM_data() are we just overwriting the corrupted data with a random data ? is there something else that's happening since 2 bit error cant be fixed.

It's SRAM. Any ECC fault is fixed by rewriting the corrupted RAM cell.

Q4. Do i need to keep the interrupts enabled in ERM as the errors generated by EIM is already handled by IVOR1 do we need the interrupt from IVOR4? was this done for some reason?

IVOR4 is used for single bit errors which will not cause IVOR1 as multibits and are automatically corrected via ECC mechanism.

Multibit fault is also latched here if occurs.

Regards,

Peter