- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 产品论坛

- :

- MCX Microcontrollers

- :

- SPI Serial Boot Issues on MIMXRT595-EVK

SPI Serial Boot Issues on MIMXRT595-EVK

I am working with the MIMXRT595-EVK evaluation board and am attempting to use the ROM bootloader for serial download via the SPI interface. My goal is to communicate with the bootloader and download an application image through SPI, similar to how it is commonly done via UART.

Here is my current situation:

First, I successfully verified that the ROM bootloader is functional by performing a serial download via UART(J26)

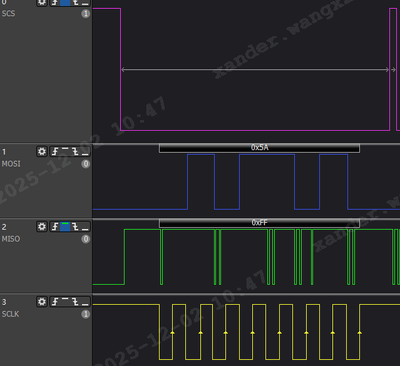

Then I am now trying to use the SPI interface on header J36 (pins 1-CS, 3-MOSI, 5-MISO, 7-SCK) for the serial download process.When I probe the signals with an oscilloscope, the MISO line (J36, pin 5) shows an incorrect and jittery waveform during the ISP communication attempt.

Questions and Points of Confusion:

I suspect that the SPI signals from the J36 header may not be properly routed to the MCU pins used by the ROM boot.

I have noticed references to a J10 header in the board documentation, but it is not physically present on my EVK.

In summary, since UART-based serial download works flawlessly, the issue appears to be specific to the SPI hardware path. My primary questions concern the correct jumper settings for J36 to enable the SPI serial downloader and the relevance of the documented but missing J10 header.

已解决! 转到解答。

Hi @wx1 ,

Thank you so much for your interest in our products and for using our community.

Could you please help clarify the following regarding your use of the MIMXRT595-EVK board:

- SW7 Pin Settings – Which boot mode are you currently using?

- Communication Tool – Which tool or interface are you using to communicate with the board?

Wish it helps you.

If you still have question about it, please kindly let me know.

Best Regards

MayLiu

Hi @wx1 ,

Thank you so much for your interest in our products and for using our community.

Could you please help clarify the following regarding your use of the MIMXRT595-EVK board:

- SW7 Pin Settings – Which boot mode are you currently using?

- Communication Tool – Which tool or interface are you using to communicate with the board?

Wish it helps you.

If you still have question about it, please kindly let me know.

Best Regards

MayLiu