- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- MCUXpresso Software and Tools

- :

- MCUXpresso IDE

- :

- Putting large buffers in external SDRAM

Putting large buffers in external SDRAM

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I want to place large data buffers in external on-board SDRAM. I already have a 4 MB .noinit section there for new fimware downloads, which I created this way:

__NOINIT(BOARD_SDRAM_NONCACHEABLE) __attribute__ ((aligned)) uint8_t httpsResponseBody[ 4 * 1024 * 1024 ];

Now I want another, smaller buffer (16 kB) and tried

__BSS(BOARD_SDRAM_CACHEABLE) __attribute__ ((aligned)) uint8_t assetsEscrow[ 16 * 1024 ];

But the linker complains

c:/nxp/mcuxpressoide_11.3.0_5222/ide/plugins/com.nxp.mcuxpresso.tools.win32_11.3.0.202008311133/tools/bin/../lib/gcc/arm-none-eabi/9.3.1/../../../../arm-none-eabi/bin/ld.exe: F1721_KAS.axf section `.bss_RAM5' will not fit in region `SRAM_OC'

c:/nxp/mcuxpressoide_11.3.0_5222/ide/plugins/com.nxp.mcuxpresso.tools.win32_11.3.0.202008311133/tools/bin/../lib/gcc/arm-none-eabi/9.3.1/../../../../arm-none-eabi/bin/ld.exe: region `SRAM_OC' overflowed by 3541460 bytes

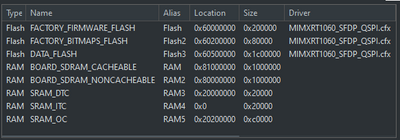

Here's my memory map:

I've read the chapter in the IDE (MCUXpresso IDE v11.3.0 [Build 5222] [2021-01-11])

User Guide on Memory Configuration and Linker Scripts, but I can't seem to specify that I want assetsEscrow to go into BOARD_SDRAM_CACHEABLE.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It is very difficult to tell with the small snippets you have provided, but the linker is not complaining about BOARD_SDRAM_CACHEABLE, but about SRAM_OC (aka RAM5), so there must be something else in your code that is causing some data to be placed there.

I also see that your have defined BOARD_SDRAM_CACHEABLE as your first RAM block. This makes it the default RAM block, so is where all of you standard program data will be placed. If this is not what you want, you will need to sort the defined order of your RAM blocks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It is very difficult to tell with the small snippets you have provided, but the linker is not complaining about BOARD_SDRAM_CACHEABLE, but about SRAM_OC (aka RAM5), so there must be something else in your code that is causing some data to be placed there.

I also see that your have defined BOARD_SDRAM_CACHEABLE as your first RAM block. This makes it the default RAM block, so is where all of you standard program data will be placed. If this is not what you want, you will need to sort the defined order of your RAM blocks.