- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- QorIQ Processing Platforms

- :

- Layerscape

- :

- Rx echo with lpuart on LS1027A

Rx echo with lpuart on LS1027A

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Rx echo with lpuart on LS1027A

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello. I'm using processor LS1027A and serial driver fsl_lpuart from linux-5.4.47-rt28. The driver says it doesn't support setting the RS485 configuration receiving during transmiting (RX_DURING_TX). Is it possible to disable the RX_DURING_TX? Or is it not implemented due to some peripheral limitation? We need this "echo" configurable for our application.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, sorry for the delay in answering. I managed to solve this problem by clearing some flags and fifo Rx data buffer. I also made some conditions with RTS flag.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Usually disabling RX during TX is not needed for RS485. Most application uses RS485 is half-duplex by using two wires.

See the Sections 23.3.1.7 and 23.4.2.3 in the LS1028A Reference Manual:

https://www.nxp.com/webapp/Download?colCode=LS1028ARM

These Sections contains the following:

RTS asserts one bit time before the start bit is transmitted. RTS deasserts one bit time after all characters in the transmitter data buffer and shift register are completely sent, including the last stop bit.

This signal is used for switching RS485 transceiver.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

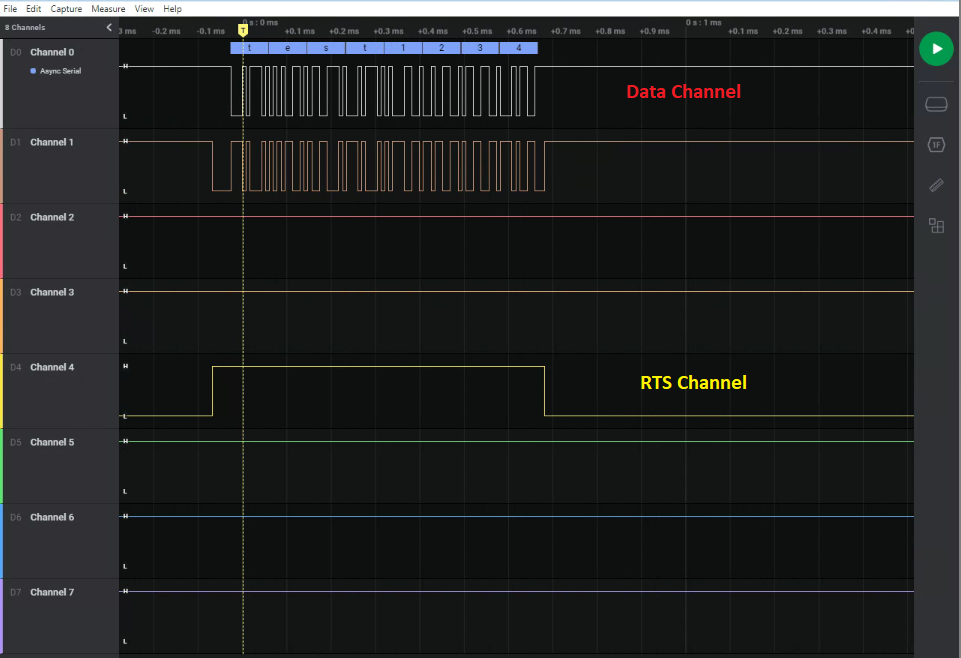

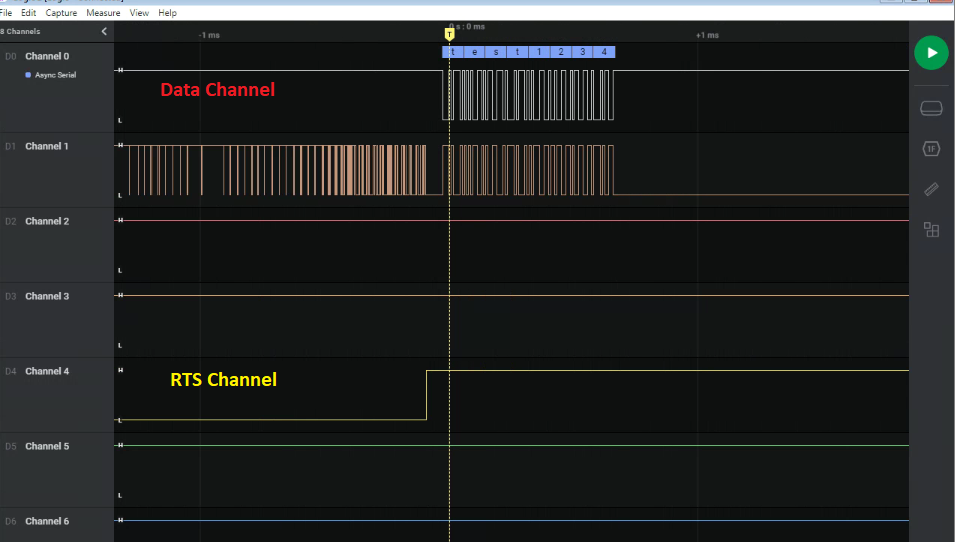

Hello, thanks for your answer, but my question isn't in that sense that you understood. I will explain in more detail what I'm doing and what I really need to know. First of all, the flow control is being made through manual control of the gpio RTS pin and the behavior is being expected as shown in the image below.

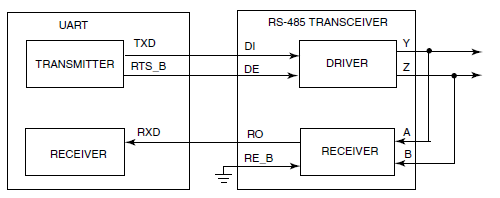

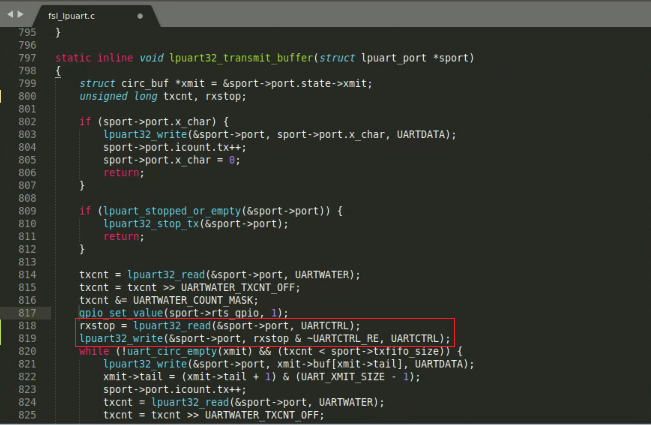

That is, in this case, the DE of the transceiver is enabled through a GPIO of the processor and not through the RTS_B of the transmitter.

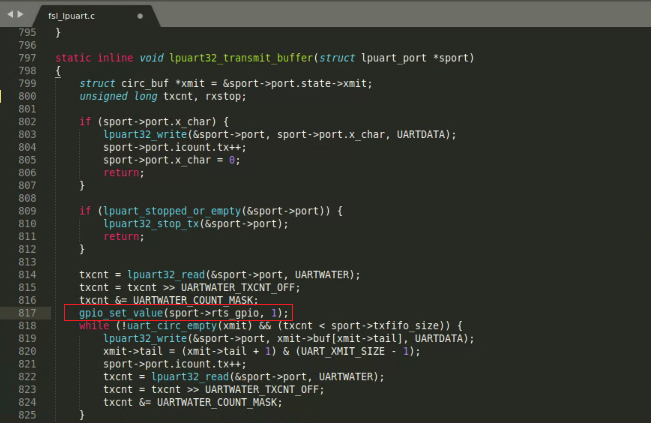

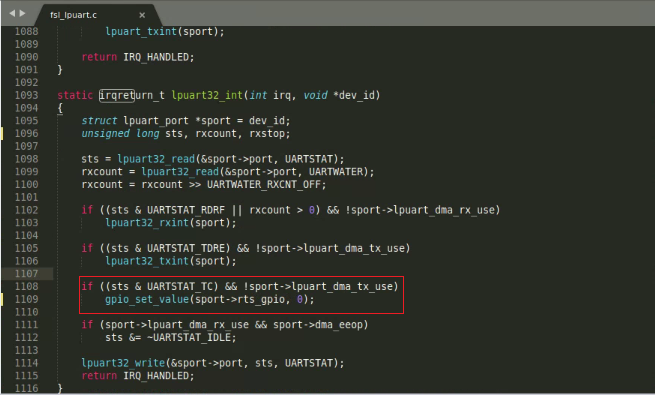

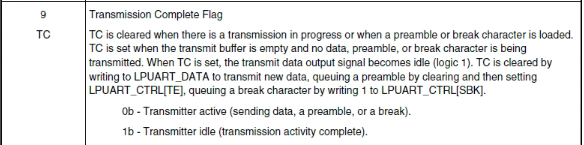

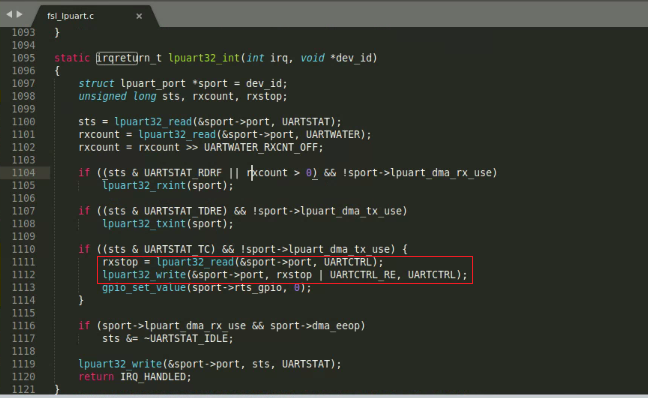

Just before the transmission happens, the RTS pin is set to high logic level and, after the end of the transmission, is set to low logic level again. I did this RTS control into the driver, set to high in the function of transmission (lpuart32_transmit_buffer()) and setting to low in the event of interrupt that is called when the transmission is complete (I used the ninth bit of the LPUART Status Register [UARTSTAT_TC]).

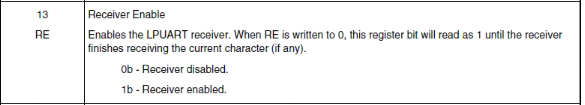

Now, I need to transmit and I don't want the reception to see what I've just transmitted. So, I tried to disable the reception just after enabling the RTS and just before starting the transmission. I enable the reception again when the transmission gets complete and just before RTS becomes disabled again. I used the thirteenth bit of the LPUART Control Register (UARTCTRL_RE) to enable and disable the reception.

The problem is when I disable the reception, the event of complete transmission doesn't occur and, consequently, RTS isn't disabled again and reception also isn't enabled. This causes no more data to be received.

So, what I need to do is disabling the reception while occurs a transmission. My questions are: can I work with the reception this way, directly changing the register? Why doesn't the event of transmission complete occurs when the reception is disabling?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Is your command sequence the following?

(1). Wait setting the UARTSTAT_TC bit.

(2). Clear the GPIO_RTS bit

(3). Set the UARTCTRL_RE bit for enabling data receiving.

(4). If there are data for transmit, clear the UARTCTRL_RE bit.

(5). Set GPIO_RTS bit

(6). transmit data

(7). return to (1)

Is the UARTSTAT_TC bit not set if the UARTCTRL_RE bit is cleared?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Actually, the UARTSTAT_TC interrupts the processor. This is the true sequence:

(1). If there are data for transmitting, set GPIO_RTS bit

(2) Clear the UARTCTRL_RE bit. So that no more data is received.

(3). transmit data

(4). When the transmission is completed, UARTSTAT_TC is set and interruption is handled.

(5). In the interruption handler, set the UARTCTRL_RE bit for enabling data receiving.

(6) In the interruption handler, clear the GPIO_RTS bit

(7). return to (1)

Steps to perform transmission with ECHO: 1, 3, 4, 6, 7

Steps to perform transmission without ECHO: 1, 2, 3, 4, 5, 6, 7

The problem is that when step 2 is performed, step 4 will not occur.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Test your board is your command sequence is changed.

(1). If there are data for transmitting, Clear the UARTCTRL_RE bit. So that no more data is received.

(2) set GPIO_RTS bit

(3). transmit data

(4). When the transmission is completed, UARTSTAT_TC is set and interruption is handled.

(5). In the interruption handler, set the UARTCTRL_RE bit for enabling data receiving.

(6) In the interruption handler, clear the GPIO_RTS bit

(7). return to (1)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Unfortunately, your suggestion of change the sequence didn't work.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Perhaps a delay is needed between steps 2 and 3. Also a delay is needed between steps 6 and 7.