- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- QorIQプロセッシングプラットフォーム

- :

- レイヤースケープ

- :

- Re: QorIQ EMI_MDIO controller ACK bit checking

QorIQ EMI_MDIO controller ACK bit checking

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

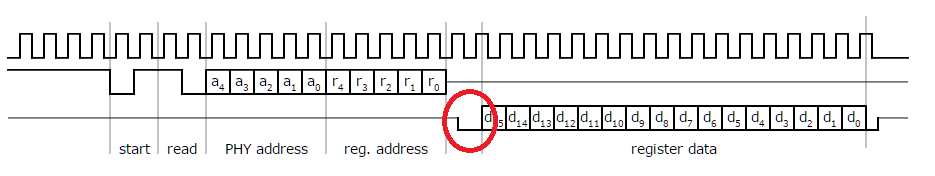

Does Ethernet Management Interface controller in QorIQ processors (namely LS1021A and T1040) check the low level on the MDIO line during the second turnaround bit (ACK) for read transactions? What if an external PHY won't set this bit low? Will the read transaction be aborted by controller or it will be completed as normal?

BR,

Denis

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Devices with eTSEC always go ahead and return what they get from the

line, regardless of TA. DPAA-enabled devices have a means to report

that the PHY didn't respond and data is not valid, see the description

of MDIO_CFG[MDIO_RD_ER] bit in your processor DPAARM.

Note that you cannot rely on u-Boot mdio read command output because

u-Boot MDIO read procedures don't report errors, see memac_mdio_read() in

memac_phy.c and tsec_local_mdio_read() in fsl_mdio.c

LS1043A is a special case. It does implement MDIO_CFG[MDIO_RD_ER],

but it is affected by erratum A-007900. Refer to the errata list

for details.

Have a great day,

Platon

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Devices with eTSEC always go ahead and return what they get from the

line, regardless of TA. DPAA-enabled devices have a means to report

that the PHY didn't respond and data is not valid, see the description

of MDIO_CFG[MDIO_RD_ER] bit in your processor DPAARM.

Note that you cannot rely on u-Boot mdio read command output because

u-Boot MDIO read procedures don't report errors, see memac_mdio_read() in

memac_phy.c and tsec_local_mdio_read() in fsl_mdio.c

LS1043A is a special case. It does implement MDIO_CFG[MDIO_RD_ER],

but it is affected by erratum A-007900. Refer to the errata list

for details.

Have a great day,

Platon

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Platon,

unfortunately I can't find the A-007900 erratum, neither at the LS1043A's Document page: QorIQ® Layerscape 1043A|NXP, nor by google.

Basically, I understand DPAA-enabled devices return what they get from the line plus (in case of Clause 22) true/false information in MDIO[MDIO_RD_ER] register if correct TA by PHY has been provided, correct?

Regarding the A-007900, can You, please, give me an advice how to obtain it or can You share the information about LS1043A's exception from the rule through the forum?

--- UPDATE ---

Following the forum threadhttps://community.nxp.com/message/845707 I assume, to acquire LS1043A's errata, I have to create Service Request or contact our local NXP dealer.

------------------

Thanks,

Cyril

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Denis,

do You have any progress regarding the QorIQ (LS1043A in my case) MDIO ACK checking? If so, please let me know.

Thanks.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Cyril,

I still have no info regarding LS1 family.

As for T1040, I have confirmed experimentally that it doesn't check the ACK bit during read transactions at least for clause 22 PHY. I have used the "mii read" command in U-Boot; it returns a correct result with no regard to the ACK bit state set by PHY. I have not checked clause 45 PHY read ("mdio read" command).

- Question for NXP:

Would you at least confirm the similarity of the EMI_MDIO controllers implemented in the T1 and LS1 families?

BR,

Denis