- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- QorIQ Processing Platforms

- :

- Layerscape

- :

- LX2160ARDB hangs during early reset

LX2160ARDB hangs during early reset

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LX2160ARDB hangs during early reset

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Here is the output from serial console:

NOTICE: BL2: Built : 17:04:14, Jan 8 2020

NOTICE: BL2: v1.5(release):lx2160a-early-access-bsp0.6

ERROR: Invalid DIMM combination.

ERROR: Parsing DIMM

Error ERROR: DDR init failed.

NOTICE: Incorrect DRAM0 size is defined in platfor_def.h

This is factory configured LX2160ARDB rev2 board. The problem was first observed with CodeWarrior TAP attached that we purchased a week ago. However, the hang occurs even when CodeWarrior TAP is not attached. It happens on every single reboot.

The only way to be able to boot again is to unplug power and wait until D28 LED turns off. However, because gdb script that we want to use in order to debug linux kernel resets the board we are unable to do any debugging.

(gdb) source ~/lx2160.gdb

Configuring the debug probe

Connecting to LX2160A

connected successfully Halt system

Execute target initialization...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I also compiled debug atf; so a little more info is printed. Below again good (after power cable unplug) vs. bad boot (reset):

INFO: Index = 0 with loc_nod=13 and input nod=13

INFO: Index = 0 with loc_nod=13 and input nod=13

INFO: Index = 0 with loc_nod=13 and input nod=30

INFO: Index = 1 with loc_nod=30 and input nod=30

INFO: Index = 0 with loc_nod=13 and input nod=30

INFO: Index = 1 with loc_nod=30 and input nod=30

INFO: Index = 0 with loc_nod=13 and input nod=13

INFO: Index = 0 with loc_nod=13 and input nod=13

INFO: Index = 0 with loc_nod=13 and input nod=30

INFO: Index = 1 with loc_nod=30 and input nod=30

INFO: Index = 0 with loc_nod=13 and input nod=30

INFO: Index = 1 with loc_nod=30 and input nod=30

INFO: Index = 0 with loc_nod=13 and input nod=13

INFO: Index = 0 with loc_nod=13 and input nod=13

INFO: Index = 0 with loc_nod=13 and input nod=30

INFO: Index = 1 with loc_nod=30 and input nod=30

INFO: Index = 0 with loc_nod=13 and input nod=30

INFO: Index = 1 with loc_nod=30 and input nod=30

INFO: Index = 0 with loc_nod=13 and input nod=13

INFO: Index = 0 with loc_nod=13 and input nod=13

INFO: Index = 0 with loc_nod=13 and input nod=30

INFO: Index = 1 with loc_nod=30 and input nod=30

INFO: Index = 0 with loc_nod=13 and input nod=30

INFO: Index = 1 with loc_nod=30 and input nod=30

INFO: Index = 0 with loc_nod=4 and input nod=17

INFO: Index = 1 with loc_nod=7 and input nod=17

INFO: Index = 2 with loc_nod=10 and input nod=17

INFO: Index = 3 with loc_nod=17 and input nod=17

INFO: Index = 0 with loc_nod=4 and input nod=17

INFO: Index = 1 with loc_nod=7 and input nod=17

INFO: Index = 2 with loc_nod=10 and input nod=17

INFO: Index = 3 with loc_nod=17 and input nod=17

INFO: RCW BOOT SRC is FLEXSPI NOR

INFO: RCW BOOT SRC is FLEXSPI NOR

NOTICE: BL2: v1.5(debug):LSDK-20.12

NOTICE: BL2: Built : 10:56:21, Apr 6 2021

INFO: time base 10 ms

WARNING: tx_byte nodev 72

WARNING: tx_byte nodev 72

NOTICE: UDIMM 18ADF2G72AZ-3G2E1

INFO: Time after parsing SPD 828 ms

INFO: Loading image id=29 at address 0x18003000

INFO: Image id=29 loaded: 0x18003000 - 0x18009bd0

INFO: Loading image id=31 at address 0x18003000

INFO: Image id=31 loaded: 0x18003000 - 0x180036d0

INFO: Loading image id=30 at address 0x18003000

INFO: Image id=30 loaded: 0x18003000 - 0x1800994c

INFO: Loading image id=32 at address 0x18003000

INFO: Image id=32 loaded: 0x18003000 - 0x180035bc

NOTICE: DDR4 UDIMM with 2-rank 64-bit bus (x8)

INFO: Time before programming controller 2990 ms

NOTICE: 32 GB DDR4, 64-bit, CL=17, ECC on, 256B, CS0+CS1

INFO: Time used by DDR driver 5837 ms

INFO: Configuring TrustZone Controller

INFO: Value of region base = ffe00000

INFO: Value of region base = 1ffe00000

INFO: Value of region base = fbe00000

INFO: Value of region base = 2880000000

INFO: Configuring TrustZone Controller

INFO: Value of region base = ffe00000

INFO: Value of region base = 1ffe00000

INFO: Value of region base = fbe00000

INFO: Value of region base = 2880000000

INFO: Configuring TrustZone Controller

INFO: Value of region base = ffe00000

INFO: Value of region base = 1ffe00000

INFO: Value of region base = fbe00000

INFO: Value of region base = 2880000000

INFO: Configuring TrustZone Controller

INFO: Value of region base = ffe00000

INFO: Value of region base = 1ffe00000

INFO: Value of region base = fbe00000

INFO: Value of region base = 2880000000

INFO: BL2: Doing platform setup

INFO: BL2: Loading image id 3

INFO: Loading image id=3 at address 0xfbe00000

INFO: Image id=3 loaded: 0xfbe00000 - 0xfbe0e17c

INFO: BL2: Loading image id 5

INFO: Loading image id=5 at address 0x82000000

INFO: Image id=5 loaded: 0x82000000 - 0x820c73e1

NOTICE: BL2: Booting BL31

INFO: Entry point address = 0xfbe00000

INFO: SPSR = 0x3cd

NOTICE: BL31: v1.5(debug):LSDK-20.12

NOTICE: BL31: Built : 10:57:32, Apr 6 2021

NOTICE: Welcome to LX2160 BL31 Phase

INFO: GICv3 without legacy support detected. ARM GICV3 driver initialized in EL3

INFO: BL31: Initializing runtime services

INFO: BL31: cortex_a72: CPU workaround for 859971 was applied

INFO: BL31: cortex_a72: CPU workaround for cve_2017_5715 was applied

INFO: BL31: cortex_a72: CPU workaround for cve_2018_3639 was applied

INFO: BL31: Preparing for EL3 exit to normal world

INFO: Entry point address = 0x82000000

INFO: SPSR = 0x3c9

U-Boot 2020.04 (Apr 06 2021 - 10:12:51 -0400)

SoC: LX2160ACE Rev2.0 (0x87360020)

Clock Configuration:

CPU0(A72):2000 MHz CPU1(A72):2000 MHz CPU2(A72):2000 MHz

CPU3(A72):2000 MHz CPU4(A72):2000 MHz CPU5(A72):2000 MHz

CPU6(A72):2000 MHz CPU7(A72):2000 MHz CPU8(A72):2000 MHz

CPU9(A72):2000 MHz CPU10(A72):2000 MHz CPU11(A72):2000 MHz

CPU12(A72):2000 MHz CPU13(A72):2000 MHz CPU14(A72):2000 MHz

CPU15(A72):2000 MHz

Bus: 700 MHz DDR: 2400 MT/s

Reset Configuration Word (RCW):

00000000: 50636338 20500050 00000000 00000000

00000010: 00000000 0c010000 00000000 00000000

00000020: 036001a0 00002580 00000000 00000096

00000030: 00000000 00000000 00000000 00000000

00000040: 00000000 00000000 00000000 00000000

00000050: 00000000 00000000 00000000 00000000

00000060: 00000000 00000000 00027000 00000000

00000070: 08b30010 00150020

Model: NXP Layerscape LX2160ARDB Board

Board: LX2160ACE Rev2.0-RDB, wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=0

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=1

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=2

i2c_init_transfer: give up i2c_regs=0x2000000

Board version: O, boot from wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=0

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=1

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=2

i2c_init_transfer: give up i2c_regs=0x2000000

invalid setting, xmap: 7

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=0

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=1

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=2

i2c_init_transfer: give up i2c_regs=0x2000000

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=0

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=1

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=2

i2c_init_transfer: give up i2c_regs=0x2000000

FPGA: v255.255

SERDES1 Reference: Clock1 = 161.13MHz Clock2 = 161.13MHz

SERDES2 Reference: Clock1 = 100MHz Clock2 = 100MHz

SERDES3 Reference: Clock1 = 100MHz Clock2 = 100MHz

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x77 retry=0

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x77 retry=1

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x77 retry=2

i2c_init_transfer: give up i2c_regs=0x2000000

PCA: failed to select proper channel

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x77 retry=0

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x77 retry=1

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x77 retry=2

i2c_init_transfer: give up i2c_regs=0x2000000

PCA: failed to select proper channel

core voltage not adjusted

DRAM: 31.9 GiB

DDR 31.9 GiB (DDR4, 64-bit, CL=17, ECC on)

DDR Controller Interleaving Mode: 256B

DDR Chip-Select Interleaving Mode: CS0+CS1

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x77 retry=0

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x77 retry=1

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x77 retry=2

i2c_init_transfer: give up i2c_regs=0x2000000

PCA: failed to select proper channel

WDT: Started with servicing (30s timeout)

Using SERDES1 Protocol: 19 (0x13)

Using SERDES2 Protocol: 5 (0x5)

Using SERDES3 Protocol: 2 (0x2)

MMC: FSL_SDHC: 0, FSL_SDHC: 1

Loading Environment from SPI Flash... SF: Detected mt35xu512aba with page size 256 Bytes, erase size 128 KiB, total 64 MiB

OK

EEPROM: wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x57 retry=0

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x57 retry=1

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x57 retry=2

i2c_init_transfer: give up i2c_regs=0x2000000

Read failed.

In: serial_pl01x

Out: serial_pl01x

Err: serial_pl01x

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=0

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=1

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=2

i2c_init_transfer: give up i2c_regs=0x2000000

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=0

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=1

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=2

i2c_init_transfer: give up i2c_regs=0x2000000

Net: wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x77 retry=0

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x77 retry=1

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x77 retry=2

i2c_init_transfer: give up i2c_regs=0x2000000

PCA: failed to select proper channel

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x75 retry=0

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x75 retry=1

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x75 retry=2

i2c_init_transfer: give up i2c_regs=0x2000000

PCA: failed to select proper channel

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x50 retry=0

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x50 retry=1

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x50 retry=2

i2c_init_transfer: give up i2c_regs=0x2000000

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x77 retry=0

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x77 retry=1

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x77 retry=2

i2c_init_transfer: give up i2c_regs=0x2000000

PCA: failed to select proper channel

CS4223: Using software initialization...

CS4223: edc/gain/equalization settings: host: CX/4dB/4dB, line: SR/4dB/4dB

FSL_MDIO1:0 is connected to DPMAC5@25g-aui. Reconnecting to DPMAC6@25g-aui

PCIe1: pcie@3400000 disabled

PCIe2: pcie@3500000 disabled

PCIe3: pcie@3600000 Root Complex: no link

PCIe4: pcie@3700000 disabled

PCIe5: pcie@3800000 Root Complex: no link

PCIe6: pcie@3900000 disabled

DPMAC2@xlaui4, DPMAC3@xgmii

Warning: DPMAC3@xgmii (eth1) using random MAC address - 52:23:68:86:bf:ca

, DPMAC4@xgmii

Warning: DPMAC4@xgmii (eth2) using random MAC address - 26:5a:83:20:8b:3e

, DPMAC5@25g-aui

Warning: DPMAC5@25g-aui (eth3) using random MAC address - aa:d9:10:eb:e1:95

, DPMAC6@25g-aui

Warning: DPMAC6@25g-aui (eth4) using random MAC address - 8e:c9:23:32:a8:51

, DPMAC17@rgmii-id [PRIME]

Warning: DPMAC17@rgmii-id (eth5) using random MAC address - f2:b5:c3:62:57:78

, DPMAC18@rgmii-id

Warning: DPMAC18@rgmii-id (eth6) using random MAC address - 7e:da:3b:bb:1a:e3

SF: Detected mt35xu512aba with page size 256 Bytes, erase size 128 KiB, total 64 MiB

device 0 offset 0x640000, size 0x80000

SF: 524288 bytes @ 0x640000 Read: OK

device 0 offset 0xa00000, size 0x300000

SF: 3145728 bytes @ 0xa00000 Read: OK

device 0 offset 0xe00000, size 0x100000

SF: 1048576 bytes @ 0xe00000 Read: OK

crc32+

fsl-mc: Booting Management Complex ... SUCCESS

fsl-mc: Management Complex booted (version: 10.24.0, boot status: 0x1)

Hit any key to stop autoboot: 0

=> reset

resetting ...

=INFO: Index = 0 with loc_nod=13 and input nod=13

INFO: Index = 0 with loc_nod=13 and input nod=13

INFO: Index = 0 with loc_nod=13 and input nod=30

INFO: Index = 1 with loc_nod=30 and input nod=30

INFO: Index = 0 with loc_nod=13 and input nod=30

INFO: Index = 1 with loc_nod=30 and input nod=30

INFO: Index = 0 with loc_nod=13 and input nod=13

INFO: Index = 0 with loc_nod=13 and input nod=13

INFO: Index = 0 with loc_nod=13 and input nod=30

INFO: Index = 1 with loc_nod=30 and input nod=30

INFO: Index = 0 with loc_nod=13 and input nod=30

INFO: Index = 1 with loc_nod=30 and input nod=30

INFO: Index = 0 with loc_nod=13 and input nod=13

INFO: Index = 0 with loc_nod=13 and input nod=13

INFO: Index = 0 with loc_nod=13 and input nod=30

INFO: Index = 1 with loc_nod=30 and input nod=30

INFO: Index = 0 with loc_nod=13 and input nod=30

INFO: Index = 1 with loc_nod=30 and input nod=30

INFO: Index = 0 with loc_nod=13 and input nod=13

INFO: Index = 0 with loc_nod=13 and input nod=13

INFO: Index = 0 with loc_nod=13 and input nod=30

INFO: Index = 1 with loc_nod=30 and input nod=30

INFO: Index = 0 with loc_nod=13 and input nod=30

INFO: Index = 1 with loc_nod=30 and input nod=30

INFO: Index = 0 with loc_nod=4 and input nod=17

INFO: Index = 1 with loc_nod=7 and input nod=17

INFO: Index = 2 with loc_nod=10 and input nod=17

INFO: Index = 3 with loc_nod=17 and input nod=17

INFO: Index = 0 with loc_nod=4 and input nod=17

INFO: Index = 1 with loc_nod=7 and input nod=17

INFO: Index = 2 with loc_nod=10 and input nod=17

INFO: Index = 3 with loc_nod=17 and input nod=17

INFO: RCW BOOT SRC is FLEXSPI NOR

INFO: RCW BOOT SRC is FLEXSPI NOR

NOTICE: BL2: v1.5(debug):LSDK-20.12

NOTICE: BL2: Built : 10:56:21, Apr 6 2021

INFO: time base 10 ms

WARNING: I2C arbitration lost

WARNING: I2C arbitration lost

WARNING: I2C arbitration lost

WARNING: I2C arbitration lost

WARNING: I2C arbitration lost

WARNING: I2C arbitration lost

WARNING: I2C arbitration lost

WARNING: I2C arbitration lost

ERROR: Invalid DIMM combination.

ERROR: Parsing DIMM Error

ERROR: DDR init failed.

NOTICE: Incorrect DRAM0 size is defined in platfor_def.h

INFO: Configuring TrustZone Controller

INFO: Value of region base = 7fdfffea

ASSERT: drivers/arm/tzc/tzc400.c:190

Seems the problems first start happening with these warnings: "WARNING: I2C arbitration lost"

They are coming from here: wait_for_state.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I just confirmed with the testing team, we never reproduced this problem on LX2160ARDB target boards in our board farm.

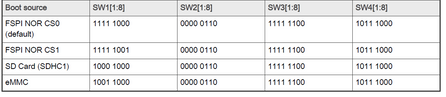

Please refer to the following switch setting for LX2160ARDB Rev 2.

If your problem remains, please contact your local FAE to exchange for another lX2160ARDB demo board, it seems that there is hardware problem with DDR PHY on your target board.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, the switches are in correct position. I will contact FAE.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please update u-boot to the latest LSDK 2012.

$ wget

https://www.nxp.com/lgfiles/sdk/lsdk2012/firmware_lx2160ardb_rev2_uboot_xspiboot.img

Under u-boot on the target board.

=> sf probe 0:0

=> tftp 0xa0000000 firmware_lx2160ardb_rev2_uboot_xspiboot.img

=> sf erase 0x0 +$filesize && sf write 0xa0000000 0x0 $filesize

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This did not help:

NOTICE: BL2: v2.3():v2.3-LSDK-20.12

NOTICE: BL2: Built : 04:32:46, Dec 11 2020

NOTICE: UDIMM 18ADF2G72AZ-3G2E1

NOTICE: DDR4 UDIMM with 2-rank 64-bit bus (x8)

NOTICE: 32 GB DDR4, 64-bit, CL=22, ECC on, 256B, CS0+CS1

NOTICE: BL2: Booting BL31

NOTICE: BL31: v2.3():v2.3-LSDK-20.12

NOTICE: BL31: Built : 04:36:09, Dec 11 2020

NOTICE: Welcome to LX2160ARDB BL31 Phase

U-Boot 2020.04-gf46a944f71 (Dec 11 2020 - 04:35:59 +0800)

SoC: LX2160ACE Rev2.0 (0x87360020)

Clock Configuration:

CPU0(A72):2200 MHz CPU1(A72):2200 MHz CPU2(A72):2200 MHz

CPU3(A72):2200 MHz CPU4(A72):2200 MHz CPU5(A72):2200 MHz

CPU6(A72):2200 MHz CPU7(A72):2200 MHz CPU8(A72):2200 MHz

CPU9(A72):2200 MHz CPU10(A72):2200 MHz CPU11(A72):2200 MHz

CPU12(A72):2200 MHz CPU13(A72):2200 MHz CPU14(A72):2200 MHz

CPU15(A72):2200 MHz

Bus: 750 MHz DDR: 3200 MT/s

Reset Configuration Word (RCW):

00000000: 5883833c 24580058 00000000 00000000

00000010: 00000000 0c010000 00000000 00000000

00000020: 036001a0 00002580 00000000 00000096

00000030: 00000000 00000000 00000000 00000000

00000040: 00000000 00000000 00000000 00000000

00000050: 00000000 00000000 00000000 00000000

00000060: 00000000 00000000 00027000 00000000

00000070: 08b30010 00150020

Model: NXP Layerscape LX2160ARDB Board [113/492]

Board: LX2160ACE Rev2.0-RDB, wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=0

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=1

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=2

i2c_init_transfer: give up i2c_regs=0x2000000

Board version: O, boot from wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=0

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=1

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=2

i2c_init_transfer: give up i2c_regs=0x2000000

invalid setting, xmap: 7

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=0

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=1

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=2

i2c_init_transfer: give up i2c_regs=0x2000000

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=0

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=1

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=2

i2c_init_transfer: give up i2c_regs=0x2000000

FPGA: v255.255

SERDES1 Reference: Clock1 = 161.13MHz Clock2 = 161.13MHz

SERDES2 Reference: Clock1 = 100MHz Clock2 = 100MHz

SERDES3 Reference: Clock1 = 100MHz Clock2 = 100MHz

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x77 retry=0

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x77 retry=1

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x77 retry=2

i2c_init_transfer: give up i2c_regs=0x2000000

PCA: failed to select proper channel

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x77 retry=0

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x77 retry=1

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x77 retry=2

i2c_init_transfer: give up i2c_regs=0x2000000

PCA: failed to select proper channel

core voltage not adjusted

DRAM: 31.9 GiB

DDR 31.9 GiB (DDR4, 64-bit, CL=22, ECC on)

DDR Controller Interleaving Mode: 256B

DDR Chip-Select Interleaving Mode: CS0+CS1

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x77 retry=0

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x77 retry=1

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x77 retry=2

i2c_init_transfer: give up i2c_regs=0x2000000

PCA: failed to select proper channel

WDT: Started with servicing (30s timeout)

Using SERDES1 Protocol: 19 (0x13)

Using SERDES2 Protocol: 5 (0x5)

Using SERDES3 Protocol: 2 (0x2)

MMC: FSL_SDHC: 0, FSL_SDHC: 1

Loading Environment from SPI Flash... SF: Detected mt35xu512aba with page size 256 Bytes, erase size 128 KiB, total 64 MiB

*** Warning - bad CRC, using default environment

EEPROM: wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x57 retry=0

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x57 retry=1

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x57 retry=2

i2c_init_transfer: give up i2c_regs=0x2000000

Read failed.

In: serial_pl01x

Out: serial_pl01x

Err: serial_pl01x

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=0

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=1

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=2

i2c_init_transfer: give up i2c_regs=0x2000000

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=0

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=1

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x66 retry=2

i2c_init_transfer: give up i2c_regs=0x2000000

Net: wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x77 retry=0

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x77 retry=1

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x77 retry=2

i2c_init_transfer: give up i2c_regs=0x2000000

PCA: failed to select proper channel

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x75 retry=0

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x75 retry=1

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x75 retry=2

i2c_init_transfer: give up i2c_regs=0x2000000

PCA: failed to select proper channel

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x50 retry=0

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x50 retry=1

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x50 retry=2

i2c_init_transfer: give up i2c_regs=0x2000000

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x77 retry=0

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x77 retry=1

wait_for_sr_state: Arbitration lost sr=13 cr=18 state=202

i2c_init_transfer: failed for chip 0x77 retry=2

i2c_init_transfer: give up i2c_regs=0x2000000

PCA: failed to select proper channel

CS4223: Using software initialization...

CS4223: edc/gain/equalization settings: host: CX/4dB/4dB, line: SR/4dB/4dB

FSL_MDIO1:0 is connected to DPMAC5@25g-aui. Reconnecting to DPMAC6@25g-aui

PCIe1: pcie@3400000 disabled

PCIe2: pcie@3500000 disabled

PCIe3: pcie@3600000 Root Complex: no link

PCIe4: pcie@3700000 disabled

PCIe5: pcie@3800000 Root Complex: no link

PCIe6: pcie@3900000 disabled

DPMAC2@xlaui4

Warning: DPMAC2@xlaui4 (eth0) using random MAC address - fa:25:17:68:17:24

, DPMAC3@xgmii

Warning: DPMAC3@xgmii (eth1) using random MAC address - 8e:c4:cc:91:fa:02

, DPMAC4@xgmii

Warning: DPMAC4@xgmii (eth2) using random MAC address - b6:2f:89:0b:1e:3a

, DPMAC5@25g-aui

Warning: DPMAC5@25g-aui (eth3) using random MAC address - 32:a6:b3:b0:78:9e

, DPMAC6@25g-aui

Warning: DPMAC6@25g-aui (eth4) using random MAC address - d6:27:fe:c0:9a:0f

, DPMAC17@rgmii-id

Warning: DPMAC17@rgmii-id (eth5) using random MAC address - 7a:7a:34:30:a9:4a

, DPMAC18@rgmii-id

Warning: DPMAC18@rgmii-id (eth6) using random MAC address - 56:dc:08:d9:b0:1e

SF: Detected mt35xu512aba with page size 256 Bytes, erase size 128 KiB, total 64 MiB

device 0 offset 0x640000, size 0x80000

SF: 524288 bytes @ 0x640000 Read: OK

device 0 offset 0xa00000, size 0x300000

SF: 3145728 bytes @ 0xa00000 Read: OK

device 0 offset 0xe00000, size 0x100000

SF: 1048576 bytes @ 0xe00000 Read: OK

crc32+

fsl-mc: Booting Management Complex ... SUCCESS

fsl-mc: Management Complex booted (version: 10.24.0, boot status: 0x1)

Hit any key to stop autoboot: 0

=>

=>

=> reset

resetting ...

=>NOTICE: BL2: v2.3():v2.3-LSDK-20.12

NOTICE: BL2: Built : 04:32:46, Dec 11 2020

ERROR: Invalid DIMM combination.

ERROR: Parsing DIMM Error

ERROR: DDR init failed.

NOTICE: Incorrect DRAM0 size is defined in platform_def.h

<hang>- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I ran into the same error with the latest build of uefi and ended up building my own, and the issue went away once I validated the DIMM speed settings and CPU frequency (since we can change those values, and the CPU can be overclocked in some instances, and RAM can run faster than stock in some instances).

So I'd recommend re-checking your CPU clock speed, BUS speed, and RAM variables that determine which file to download for the UEFI image. It may be that your RAM is not the same speed you remember, as an example the 3200 Mhz image will not boot for 2933 Mhz DIMMs - for that you would want the 2900 variable UEFI image file.