- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- QorIQ Processing Platforms

- :

- Layerscape

- :

- Re: LS1043ARGW SD TFA boot problem

LS1043ARGW SD TFA boot problem

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have LS1043ARGW custom boards and LS1043ARDB-PD boards. I am trying to boot from an sd card.

And I need OP-TEE, so I have to boot with TFA. However, there is a problem that the boot does not work. So I built it as tfa, not SECURE_tfa. Of course the ASK binary works fine.

1. u-boot (Needed for building atf)

I made u-boot patch file with reference to RGW u-boot. And patched to u-boot LSDK-20.04.

Then I set to ls1043argw_tfa_config and built.

2. atf

atf LSDK-20.04 was built using the following options:

PLAT=ls1043ardb

BOOT_MODE=sd

RCW=(ls1043ardb-sdboot-rcw.bin) <- attached file

BL33=u-boot.bin

FIPTOOL=tools/fiptool/fiptool

CREATE_PBL=/plat/nxp/tools/create_pbl

BYTE_SWAP=/plat/nxp/tools/byte_swap

DEBUG=1

3. write to sd card

bl2_sd.pbl and fip.bin generated by building atf were written to the sd card.

| Write to SD |

|---|

dd if=/dev/zero of=/dev/mmcblk0 bs=1M count=10 dd if=bl2_sd.pbl of=/dev/mmcblk0 bs=512 seek=8 |

4. boot

When booting this sd card from RDB

| RDB boot log |

|---|

INFO: RCW BOOT SRC is SD/EMMC NOTICE: 2 GB DDR4, 32-bit, CL=11, ECC off U-Boot 2019.10 (May 07 2020 - 07:46:23 +0100) SoC: LS1043AE Rev1.1 (0x87920011) EEPROM: NXID v1 |

but when booting from RGW

| RGW boot log |

|---|

?NFO: RCW BOOT SRC is SD/EMMC NOTICE: 2 GB DDR4, 32-bit, CL=11, ECC off |

I have looked at the operation problems of eSDHC, but confirmed that it works in 1bit little-endian mode on the source.

As a result of several boot checks, the ATF confirmed that the FIP header value was read from 0x10_0000.

In the case of RDB, the FIP header read the value of 0x10_0000 correctly, but it was confirmed that RGW reads the value of 0x10_0008.

I have not yet figured out what is causing this issue.

Please help me.

best regards.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello hakjun oh,

In the TF-A boot flow, DDR initialization is not required in U-Boot. DDR initialization is a part of TF-A.

DDR init code can be added to <atf_dir>/plat/nxp/soc-<soc-name>/<soc-name>ardb/ddr_init.c.

You need to modify ddr_raw_timing in atf/plat/nxp/soc-ls1043/ls1043ardb/ddr_init.c according to your custom board.

Thanks,

Yiping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello hakjun oh,

In the TF-A boot flow, DDR initialization is not required in U-Boot. DDR initialization is a part of TF-A.

DDR init code can be added to <atf_dir>/plat/nxp/soc-<soc-name>/<soc-name>ardb/ddr_init.c.

You need to modify ddr_raw_timing in atf/plat/nxp/soc-ls1043/ls1043ardb/ddr_init.c according to your custom board.

Thanks,

Yiping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yiping.

So, is the RAM timing problem the reason why BL2 Image is read from 0x10_0008 when LS1043ARGW is booted?

Thanks,

hakjun oh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello hakjun oh,

Yes, DDR initialization problem is the cause.

Thanks,

Yiping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yiping.

Unfortunately, the ram timing value has been changed, but the same message is output.

The source uses the MT40A512M8HX-093E, but our custom board uses the MT40A512M8RH-083E.

The changes are as follows.

| plat/nxp/soc-ls1043/ls1043ardb/ddr_init.c |

|---|

diff --git a/plat/nxp/soc-ls1043/ls1043ardb/ddr_init.c b/plat/nxp/soc-ls1043/ls1043ardb/ddr_init.c -/* DDR model number: MT40A512M8HX-093E */ |

Did I miss something or change it wrong?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello hakjun oh,

You could use QCVS DDRv tool to validate and optimize DDR controller initialization parameters.

Would you please try your new generated ATF image on LS1043ARDB to check whether you encounter similar problem as booting from RGW?

Thanks,

Yiping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yiping.

Are you trying to boot an ATF image for RGW into RDB?

This is the RDB log in the table above, but DDR_DEBUG option enabled, it looks like this:

| RDB log with DDR_DEBUG |

|---|

픭?NFO: RCW BOOT SRC is SD/EMMC NOTICE: 2 GB DDR4, 32-bit, CL=11, ECC off

SoC: LS1043AE Rev1.1 (0x87920011) EEPROM: NXID v1 |

Thanks,

hakjun oh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello hakjun oh,

Please apply your DDR patch for LS1043ARGW on packages/firmware/atf/plat/nxp/soc-ls1043/ls1043ardb/ddr_init.c in ATF source code, then move build/firmware/atf/ and build/firmware/u-boot/, rebuild ATF image for LS1043ARDB and verify it on LS1043ARDB.

Thanks,

Yiping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yiping.

Is there anything else I can do?

Thanks,

hakjun oh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello hakjun oh,

Please check whether RCW for LS1043ARGW is correct.

Do you have CodeWarrior and CodeWarrior TAP? If yes, please create a bareboard project in CodeWarrior and check whether the sample project can run on the target board. In CodeWarrior initialization file, please modify DDR initialization parameters with your debug data, please use USE_SAFE_RCW = True in CW initialization file to use the hard-coded RCW.

Thanks,

Yiping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yiping.

Yes. The bare board project worked fine.

I think there perhaps have problem with RCW so I modified ASK's RCW to work with SDHC and booted, but the result is the same.

What shall we do next?

Reset Configuration Word (RCW):

00000000: 08100010 0a000000 00000000 00000000

00000010: 14550002 80004002 60106000 c1002000

00000020: 00000000 00000000 00000000 01030940

00000030: 00000000 00003004 00000096 00000001

Thanks,

hakjun oh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello hakjun oh,

In CodeWarrior initialization file, please configure USE_SAFE_RCW = False, please configure the target board as booting from SD card, then try whether the bareboard project can work fine.

Thanks,

Yiping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yiping.

Oops, sorry. I didn't understand the prev answer to the question well.

In the previous question, RGW booting with the USE_SAFE_RCW = True option causes the machine to hang.

| RGW booted with SAFE_RCW |

|---|

| INFO: RCW BOOT SRC is SD/EMMC INFO: RCW BOOT SRC is SD/EMMC INFO: esdhc_emmc_init INFO: Card detected successfully INFO: init done: INFO: platform clock 400000000 INFO: DDR PLL1 1600000000 INFO: DDR PLL2 0 INFO: time base 32 ms INFO: Parse DIMM SPD(s) INFO: cal cs INFO: cs_in_use = 1 INFO: cs_on_dimm[0] = 1 NOTICE: Fixed DDR on board INFO: Time after p |

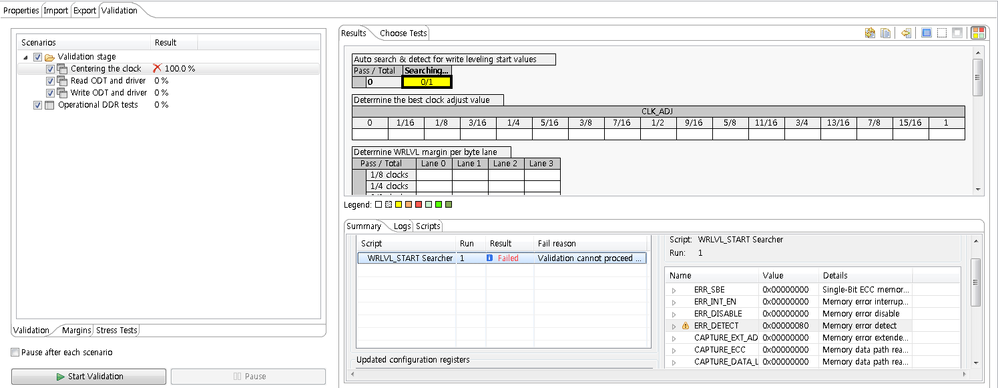

And when the diagnosis starts, an error is displayed in 2 items.

| Test Name | Info |

|---|---|

| ... | ... |

| Run target initialization script | DDR: initialization failed (ERR_DETECT = 0x00000080). |

| Test DDR memory access | Memory verification failed. First mismatch was found at address 0x80000000. Expected 'aa', but found '55'. |

| ... | ... |

But likewise, booting the RDB with the USE_SAFE_RCW = True option cause hang.

| RDB booted with SAFE_RCW |

|---|

| INFO: RCW BOOT SRC is SD/EMMC INFO: RCW BOOT SRC is SD/EMMC INFO: esdhc_emmc_init INFO: Card detected successfully INFO: init done: INFO: platform clock 400000000 INFO: DDR PLL1 1600000000 INFO: DDR PLL2 0 INFO: time base 32 ms INFO: Parse DIMM SPD(s) INFO: cal cs INFO: cs_in_use = 1 INFO: cs_on_dimm[0] = 1 NOTI |

However, the diagnosis has not error.

Thanks,

hakjun oh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please use DDRv to connect your custom board to optimize and validate your DDR configuration parameters on the custom board.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yiping.

I found something while I was looking at the board. I thought it was MT40A512M88HX-093E because it was written as MT40A512M8HX-093E in the RDB source and schematic. However, I confirmed that the FBGA codes of RDB and RGW are the same.

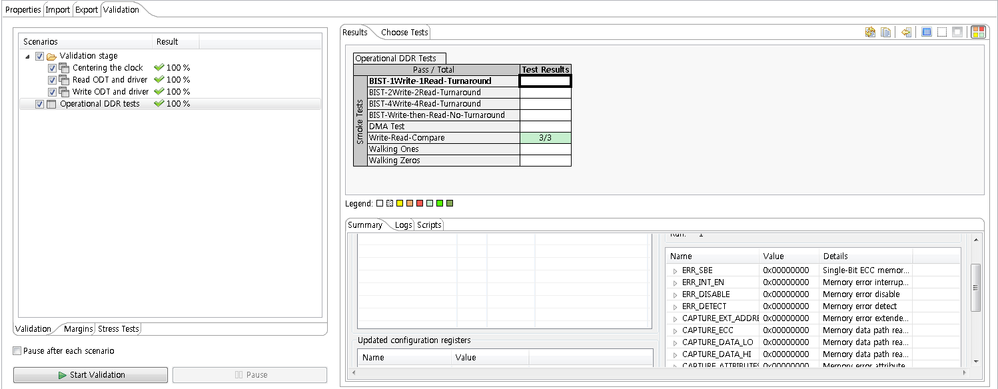

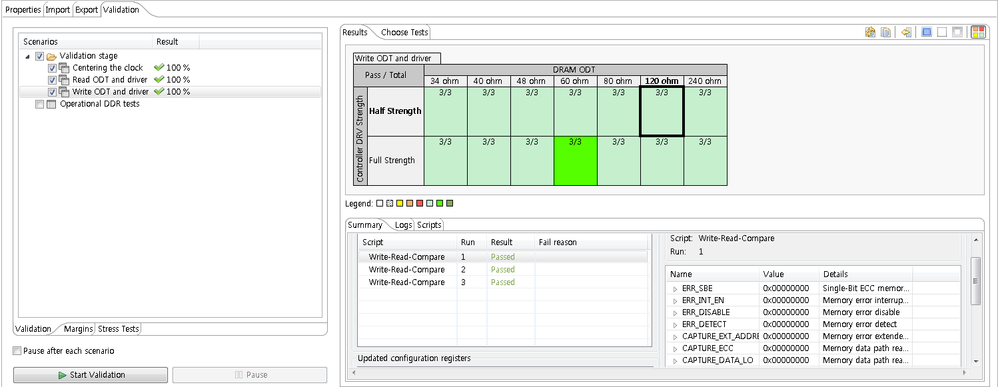

Different results were obtained when the Validation Test was performed by matching the set values using Codewarrior DDRv. In RDB, all tests are Passed, but in RGW, all tests are Failed.

| RGW DDR | RDB DDR |

|---|---|

|  |

|  |

The more I do, the more I can't figure out the cause. What more should I do?

I will continue to validate DDR configuration parameters.

Thanks,

hakjun oh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yiping.

I found reason of failed DDR validation in Codewarrior DDRv. It should have set DQ values. I didn't know if there was this option.

Either way, the results are good. Now I should check if there is any DQ setting in the ATF source.

| RGW DDR Validation |

|---|

|

Thanks,

hakjun oh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yiping.

The problem has been resolved.

| plat/nxp/soc-ls1043/ls1043ardb/ddr_init.c |

|---|

diff --git a/plat/nxp/soc-ls1043/ls1043ardb/ddr_init.c b/plat/nxp/soc-ls1043/ls1043ardb/ddr_init.c

/* DDR model number: MT40A512M8HX-093E */ |

Thank you very much.

hakjun oh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Hakjunoh,

I have same problem. Can you share me how to mapping data?

Thanks so much!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yiping.

I'm not sure what I understand, but DDR patch for LS1043ARGW applied to flexbuilder. And rebuilded u-boot and atf.

The rebuilt image was written to SD and booted from LS1043ARDB.

The boot log is:

| Boot log on LS1043ARDB with DDR patch applied. |

|---|

NOTICE: Fixed DDR on board NOTICE: 2 GB DDR4, 32-bit, CL=11, ECC off

SoC: LS1043AE Rev1.1 (0x87920011) MMC read: dev # 0, block # 18944, count 128 ... EEPROM: NXID v1 |

Thanks,

hakjun oh