- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- General Purpose Microcontrollers

- :

- LPCware Archive Content

- :

- LPC43XX Dual Core Examples

LPC43XX Dual Core Examples

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

LPC43XX Dual Core Examples

LPC43XX Dual Core Examples

1. Important Notes

1. Please read the build section of Libraries and Example before building anything

2. Never give batch build with all the items selected.

3. When building an example make sure the M0 image is built and ready before building the M4 image

4. Read the latest release notes before proceeding with this document

2. Introduction

This document will provide the instructions and information required to use the LPC43xx dual core demos. The source files can be either obtained from the git server or can be downloaded attached as a compressed zip file.

2.1 Dual Core in LPC43XX

The LPC43xx is an ARM M4/M0 based dual core microcontroller. The SoC comes with Internal IRAM/Flash of various sizes. Please read the LPC43xx user manual and the board user manual carefully before starting to use the dual core demos on any of the LPC43XX board.

2.2 Hardware requirements

- Keil MCB4300 Development board

- Serial cable or USB to serial port dongle

- Keil uLink-2 or Keil uLink-Pro or Segger J-Link debugger (for ARM Cortex M devices)

- Development PC/Laptop (Host Machine)

- Keil uVision IDE MDK-ARM tool-chain (version 4.54 or above)

- Terminal emulation software (Teraterm recommended)

- Windows OS in which Keil tool can run (Windows 7 recommended)

2.3 Software requirements

3. Directory Structure

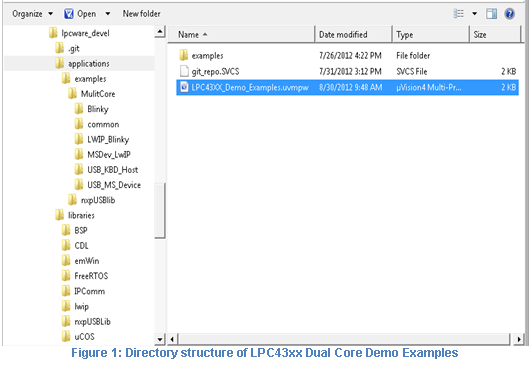

The software has two main directories, the “library” directory and the “applications” directory. It follows the same directory structure as followed by the “NXPUSBLibrary”. Inside the “applications” directory is the main Keil multi project workspace LPC43xx_Demo_Examples.uvmpw could be found as shown in Figure 1: Directory structure of LPC43xx Dual Core Demo Examples. The library directory has the following libraries[1] in it

- CDL (for LPC43XX)

- BSP (for KEIL MCB4357 board)

- nxpUSBLib (for Host and Device)

- FreeRTOS

- IPComm

The example directory will have both the nxpUSBlib, and the MultiCore examples. This document will only have the details about the MultiCore examples. The Following MultiCore examples can be found under examples directory.

- Common (Not an example in itself but is used by all the examples)

- USB_KBD_HostBlinky)

- USB_MS_Device (USB Mass Storage device and Blinky)

4. Libraries

4.1 Building Library

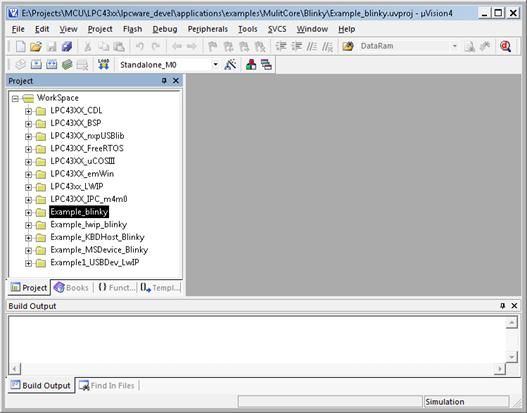

Open the Keil uVision multiple project workspace by double clicking on the “LPC43xx_Demo_Examples.uvmpw”. The project workspace opens in the uVision IDE, as shown in Figure 2: LPC43xx_Demo_Example in Keil uVision Workspace.

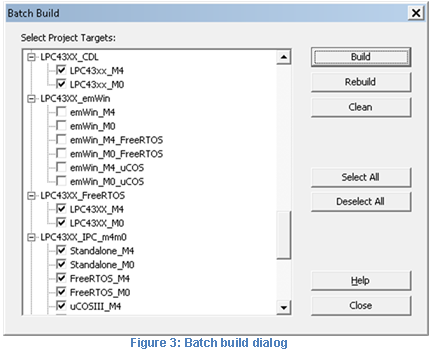

For building the libraries it is recommended to use the batch build option provided by Keil. Select “Project” from the menu (on top of the IDE), followed by “Batch build…”, which will open the batch build window as shown in Figure 3: Batch build dialog. To build a specific library all the other selections must be cleared, this can be done by clicking on “Deselect All” button located in the left side of the dialog. Now to build, say CDL library, the appropriate library configurations must be selected [Example, for CDL “LPC43xx_M4 and LPC43xx_M0” must be selected]. Clicking the build button located at the top left side of the dialog will build the selected library. Each project is provided with a README.TXT file that will help the user to know more about the various configurations and how to use them.

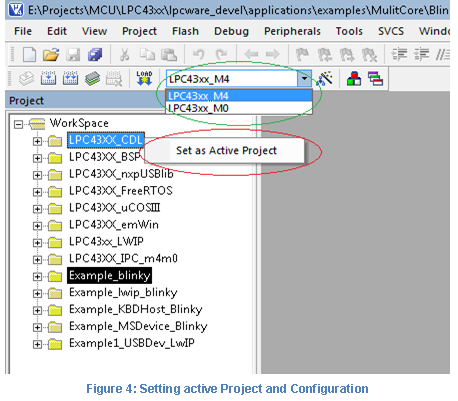

The library can also be built configuration by configuration. To do so, one must first make that project active by right clicking on the library and selecting the “Set as Active Project” from the menu that pops up (marked red in Figure 4: Setting active Project and Configuration), now select a configuration from the pull down menu (marked as green in Figure 4: Setting active Project and Configuration). Once the active configuration is selected press “F7” key to start the build process of the active configuration. After successful build select the next configuration and start the build process.

4.2 CDL (Common Driver Library)

4.2.1 Description

The common driver library (CDL) will have the functions with which can be used to initialize and operate on any peripheral present in the SoC. It has files that implements functions for each peripheral (lpc43xx_uart, lpc43xx_i2c etc,). The CDL also has the CMSIS sources which will have the startup code required for starting up of the SoC. The CMSIS library has 2 startup files (lpc43xx_startup.S and lpc43xx_startup_m0.S) for Cortex M4 core and Cortex M0 core respectively.

4.2.2 Configurations

The CDL supports two configurations (LPC43xx_M4 and LPC43xx_M0) one for each core

4.2.2.1 LPC43xx_M0

This configuration will build the library that could be linked and used with application that is meant to run on M0 core. This library will have the startup code for M0 core. If the users want to develop a new module they must keep in mind that all the IRQ handler names are prefixed with “M0_”.

4.2.2.2 LPC43xx_M4

This configuration will build CDL library, so that it can be linked and used by applications that are compiled for M4 core.

4.2.3 Output Files

All output files (including the object and list files) will be located under “keil_ouput” directory of the corresponding library/example

CDL_LPC43xx_M4.lib – Generated by building CDL for “LPC43xx_M4” configuration

CDL_LPC43xx_M4.lib – Generated by building CDL for “LPC43xx_M0” configuration

4.3 BSP (Board Support Package) Library

4.3.1 Description

This library has the functions required to initialize the board specific features. For example the external Flash, external DRAM, pin mux, LEDs etc. This library implements the bsp_init API that initializes the board (Recommended to call only from M4 core). This library supports two boards HITEX LPC4350 and KEIL MCB4357. The user must build the configurations only for the relevant board. Say, for example the users of HITEX 4350 board must build only HITEX4350_M0 and HITEX4350_M4, and should not build anything else. The board configuration that was build last (M0 and M4) will be considered for linking with any application.

4.3.2 Configurations

For batch building of this library it is recommended to build only two configurations (M0, M4) that belongs to the same board.

4.3.2.1 MCB4300_M0

This configuration will build the BSP library for MCB4300 board and will provide functions that can be called from M0 core. This configuration must be built only along with MCB4300_M4 and not with any other configuration.

4.3.2.2 MCB4300_M4

This configuration will build the BSP library for MCB4300 board and will provide functions that can be called from M4 core. This configuration must be built only along with MCB4300_M0 and not with any other configuration.

4.3.3 Output Files

BSP_LPC43XX_M4.lib – Library generated by building MCB4300_M4 configuration

BSP_LPC43XX_M0.lib – Library generated by building MCB4300_M0 configuration

Since we do not generate separate libraries for each board the configuration build recently will be taken for linking with the example applications.

4.4 nxpUSBlib (NXP’s USB Library)

4.4.1 Description

This library provides the USB host/device support for LPC USB based microcontrollers. The original source of this library can be found at www.lpcware.com. But it is recommended to use the sources provided along with the dual core examples (Has some bug fixes and routines required for dual core operation of this library). For more information refer to document that comes along with the library.

4.4.2 Configurations

For batch building this library it is recommended to select all the configurations.

LPC43xx_Host_M0 – Configuration that builds USB host stack for M0 core

LPC43xx_Device_M0 – Configuration that builds USB device stack for M0 core

LPC43xx_Host_M4 – Configuration that builds USB host stack for M4 core

LPC43xx_Device_M4 – Configuration that builds USB device stack for M4 core

4.4.3 Output Files

nxpUSBlib_LPC43xx_Host_M0.lib – Created by building this library for configuration LPC43xx_Host_M0

nxpUSBlib_LPC43xx_Device_M0.lib – Created by building this library for configuration LPC43xx_Device_M0

nxpUSBlib_LPC43xx_Host_M4.lib – Created by building this library for configuration LPC43xx_Host_M4

nxpUSBlib_LPC43xx_Device_M4.lib – Created by building this library for configuration LPC43xx_Device_M4

4.5 FreeRTOS

4.5.1 Description

This library is compiled of the FreeRTOS source obtained from www.freertos.org. Minimal modifications had been made to the OS files so that they will work on LPC43xx in both the cores. For more information about FreeRTOS refer www.freeRTOS.org

4.5.2 Configuration

For batch building it is recommended to select all the configurations.

4.5.2.1 LPC43xx_M0

This configuration will compile FreeRTOS library from the sources that could be run from M0 core of LPC43xx. When this configuration is selected the FreeRTOS source will read its configuration header from lpc43xx_m0_FreeRTOSConfig.h kept under config directory of the FreeRTOS library, and will use RITIMER hardware to generate the system ticks.

4.5.2.2 LPC43xx_M4

This configuration will compile FreeRTOS library from the sources that could be run from M4 core of LPC43xx. When this configuration is selected the FreeRTOS source will read its configuration header from lpc43xx_m4_FreeRTOSConfig.h kept under config directory of the FreeRTOS library.

4.5.2.3 Output Files

FreeRTOS_LPC43XX_M0.lib – Generated by building the library using LPC43xx_M0 configuration.

FreeRTOS_LPC43XX_M4.lib – Generated by building the library using LPC43xx_M4 configuration.

4.6 IPComm (Inter Processor Communication Library)

4.6.1 Description

This library provides the functions to communicate between cores (M0/M4). This is required for the applications running on both the cores. For more information about this library and usage refer Application Note AN11177: Inter Processor Communications.

4.6.2 Configuration

It is recommended to select all the configuration during the batch build.

Standalone_M0 – Building IPC library for this configuration will generate IPC functions without support from any OS and can run on M0 core

Standalone_M4 – Building IPC library for this configuration will generate IPC functions without support from any OS and can run on M4 core

FreeRTOS_M0 – Building IPC library for this configuration will generate IPC functions with FreeRTOS support and can run on M0 core

FreeRTOS_M4 – Building IPC library for this configuration will generate IPC functions with FreeRTOS support and can run on M4 core

4.6.3 Output Files

The following are the output files generated for the above configurations respectively

IPC_noOS_M0.lib

IPC_noOS_M4.lib

IPC_FreeRTOS_M0.lib

IPC_FreeRTOS_M4.lib

5. Examples

5.1 Setting up of board and debuggers

This section provides information about setting up of various board to execute the dual core examples. For now the examples support only HITEX4350 and MCB4300 boards.

5.1.1 Setting up MCB4300 board

Follow the steps below to setup the KEIL MCB4300 board to run the dual core examples

- Connect the U-Link/J-Link debugger’s 10-Pin debug port header to J6 port of the board.

- Connect the debugger to the Host PC using USB cable provided with the debugger (Debugger’s power LED should be lit after connecting)

- Connect a Serial cable (Straight cable) to the board’s P11 (UART0/3) port and connect the other end to the host PC

- Open teraterm select the COM port corresponding to the Serial Port to which the board is connected, select 115200 as the baud rate and no flow control

- Connect the USB cable’s[2] (Type-A to Micro-B) Micro-B end to the board’s Micro-B receptacle P2 (USB0) [Not to P4 USB1]

- Connect the Type-A end of the USB cable to the host PC (now the board should power ON)

5.1.2 Setting up Examples for debugging

The following steps must be executed for all the examples. It must only be carried out for M4 targets and need not have to be done for any M0 target. It is applicable only for the examples and not for the libraries.

- Select the example as active project by right clicking on it (Circled red in Figure 4: Setting active Project and Configuration)

- Select the M4 configuration from the configuration selection pull down menu (Circled green in Figure 4: Setting active Project and Configuration)

- In the project view (Located in the left side of the IDE), expand the active example by clicking on it and click on the configuration (shown with a folder icon)

- Press “Alt” key and while holding it Press and release “F7” key, this will show the options dialog for the currently selected M4 configuration

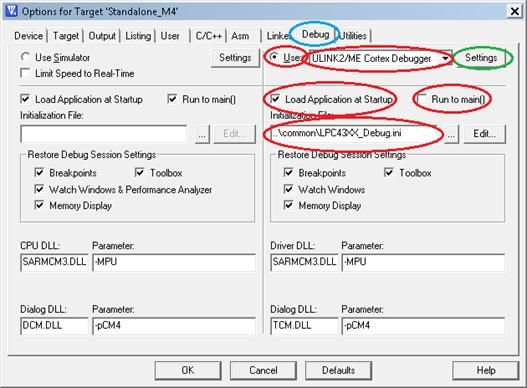

- 6. Now configure your debugger as shown in the figure (Red circles in Figure 5: Debugger configuration in Keil uVision)5. Click on the “Debug” tab located on the top of the dialog (Blue circle in Figure 5: Debugger configuration in Keil uVision)

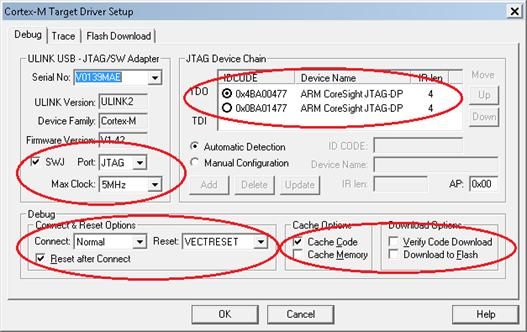

- Click on the Settings button (Green circle in Figure 5: Debugger configuration in Keil uVision) to open the debugger hardware configuration dialog as shown in Figure 7: U-Link debugger Hardware settings

- Setup the configuration[3] (shown in red circles) in the dialog as shown in Figure 6: U-Link debugger Hardware settings

- Click OK to save the configuration and close the dialog

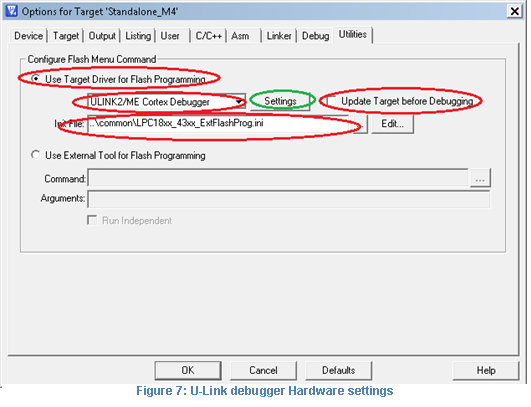

- 10. Now click on the utilities tab at the top of the options dialog (Tab next to the blue circled debug tab in Figure 5: Debugger configuration in Keil uVision)

- Now the window will look as shown in Figure 7: Keil flash configuration utility window

- Setup the configuration (red circled) in the utility window as shown in Figure 7: Keil flash configuration utility window

- Click the settings button (Green circled in Figure 7: Keil flash configuration utility window)

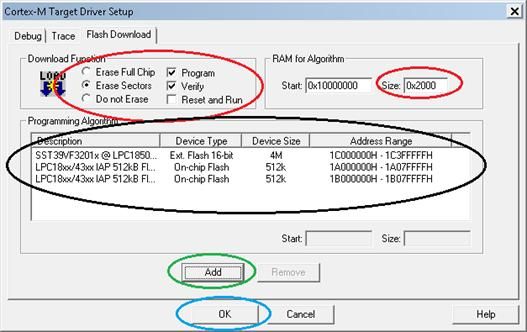

- That will open the Flash driver setup window as shown in Figure 8

- Select the configuration (Red circled) as shown in

- Click on the add button (Green Circled in Figure 8: Flash driver configuration window)

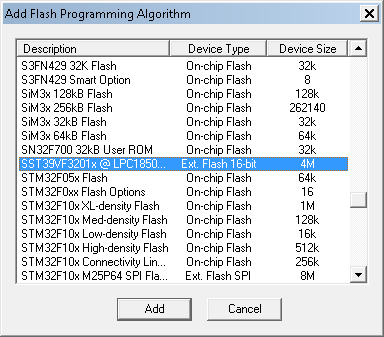

- That will open the flash programming algorithm select window as in Figure 9: Flash Programming Algorighm select window

- In the flash programming algorithm window select SST39VF3201x[4] and click “Add” button in Figure 9: Flash Programming Algorighm select window

- Repeat Step 16 to 18 for LPC18xx/43xx IAP 512kB for both 1A000000 and 1B000000 address range

- Click OK (Blue circled) as shown in Figure 8: Flash driver configuration window

- Press OK in Keil flash configuration utility window to save the configuration and exit the options window

- Repeat the steps for all the examples for all the M4 configurations

5.1.3 Building & Executing Examples

Every example will have a set of M0 configuration and M4 configurations, the user must build the M0 configuration first and then the corresponding M4 configuration. For compatible configurations please refer to the configuration table provided under each example. Once both M0 and the corresponding M4 images are built click on the debug button to start the debugging. Press “F5” key to execute the code.

to start the debugging. Press “F5” key to execute the code.

5.2 Blinky Example

5.2.1 Description

This example blinks the LED1 (Red LED in HITEX board) and LED2 (Green LED in HITEX board). The M4 core pushes the LED1 turn ON/OFF message at an interval of every 500 milliseconds and the message is popped by M0 core and based on the message it turn ON/OFF LED1. The same way M0 core pushes LED2 ON/OFF message and is popped by the M4 core and blinks the LED2 accordingly. So, on both the cores there will be two tasks running one pushes the message another pops and executes the command present in the message.

5.2.2 Configuration

M4 Configuration | M0 Configuration | Remarks |

Standalone_M4 | Standalone_M0 FreeRTOS_M0 | All configurations possible |

FreeRTOS_M4 | Standalone_M0 FreeRTOS_M0 | All configurations possible |

Table 5‑1: Blinky Example configuration

5.2.3 Expected Output

LED1 and LED2 blinks at different rates.

5.3 USB Host Stack Example (with Keyboard class driver)

Description

This example runs the USB Host stack in any of the core with the keyboard class driver. The stack running in any core will receive the keystroke and will push it to the other core via message queue. The other core will receive the message and print the key pressed to UART. It then sends an acknowledgement message to theblinky task running along with the USB host stack to toggle an LED.

5.3.1 Configuration

M4 Configuration | M0 Configuration |

USB_noOS_M4 | Blinky_noOS_M0 Blinky_FreeRTOS_M0 |

USB_FreeRTOS_M4 | Blinky_noOS_M0 Blinky_FreeRTOS_M0 |

Blinky_FreeRTOS_M4 | USB_noOS_M0 USB_FreeRTOS_M0 |

Blinky_noOS_M4 | USB_noOS_M0 USB_FreeRTOS_M0 |

Table 5‑3: USB Keyboard demo configurations

5.3.2 Expected Output

Blinks LED1 and LED2, connecting the keyboard to the host port will print the message keyboard enumerated on the COM port. Any key pressed in the keyboard will be printed on the teraterm. Key press will also toggle LED3.

5.4 USB Device Stack Example (Mass Storage Device Class)

5.4.1 Description

This example will run the USB device stack (Mass storage class) in any core while running the Blinky on both the cores. This example also has the FAT file system parser for getting the data present in the file storage area.

5.4.2 Configuration

Same as USB Keyboard demo configurations

5.4.3 Expected Output

The Host PC will enumerate the board as a USB disk and will contain a README.TXT that carries the text “USB Device demonstration”. LED1 and LED2 will be blinked by the Blinky tasks. The Mass Storage task will toggle the LED3 for every SCSI command it receives.