- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- MCUXpresso Software and Tools

- :

- LPCXpresso IDE

- :

- Re: LPCXPRESSO 8.0.0 bin file generation issue

LPCXPRESSO 8.0.0 bin file generation issue

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LPCXPRESSO 8.0.0 bin file generation issue

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, I'm using LPCOpen / LPCXpresso 8.0.0 and LPC4357 dual core application. I'm trying to create the .bin file with the post build options (the standard ones suggested by LPCXpresso). The instructions are: arm-none-eabi-size "${BuildArtifactFileName}" arm-none-eabi-objcopy -v -O binary "${BuildArtifactFileName}" "${BuildArtifactFileBaseName}.bin" checksum -p ${TargetChip} -d "${BuildArtifactFileBaseName}.bin" The M4 code compiles and runs correctly but the .bin file is large 16MB, way bigger than it should be. I tried also with simple M4 dual core examples codes. The bin file of all M4 dual core codes is always 16MB large. Do you know how I can solve this issue? Thanks Pietro

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

LPCXpresso support: You said: "There is no reason that the M4 and M0 binary data could not be located in a single flash device."

There is very good reason why you would not locate them into a single flash - memory contention. If you have both cores running from a single flash, the performance of both with drop off of a cliff.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks to all for the clarification.

I've another question: I'm interested only in the M4 part of the bin file

so, is there a way to understand where's tha last valid byte of M4 code and

where the hole of "zeros" start inside the bin file? In this way I can

easily take only the first N data of the bin file.

Thank you!

Regards

Pietro

On Mon, Jun 20, 2016 at 11:46 AM, thefallguy <admin@community.freescale.com>

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The issue here doesn't relate to Multi-Core projects, rather the suitability of a binary file format to export data from a project that spans multiple flash devices. The example described in the FAQ LPC43xx Cortex-M4 / M0 Multicore Applications discusses a variety of possibilities for the memory that could be used. There is no reason that the M4 and M0 binary data could not be located in a single flash device.

Furthermore, the scheme described leads to the creation of a single executable (.axf) that can be programmed into flash in a single operation. This is a convenience only, there is no reason that the executables for the M4 and M0 have to be contained within a single .axf file.

Yours,

LPCXpresso-Support

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

That is correct. It is not a fault of LPCXpresso, it is just the nature of a bin file. Why not create SREC or other format that supports addresses and thus will not include the holes?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for the info "The Fall Guy".

If I understand correctly the situation, it seems that if I follow the

standard procedure (related to the link pointed out by NXP) to manage dual

core projects, there's no way to have a meaningful bin file.

If I use the "mo image loader instructions", like in the examples

"dc_sa_blinky", "dc_sa_msc_ram" and "dc_sa_webserver", I can have the

correct M4 and m0 bin files.

Thanks

Pietro

On Sun, Jun 19, 2016 at 3:13 AM, lpcware <admin@community.freescale.com>

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This was answered in the 'old' forum at

Large Binary output file size | www.LPCware.com

It has probably also been migrated to this forum, but search doesn't seem as good...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Fall Guy for responding to this ... we did migrate the FAQs (the solution pointed to on LPCWare references an FAQ). All FAQs will re-drect to this site now, but the one referenced is this one (for your convenience): LPC43xx Cortex-M4 / M0 Multicore Applications

We'll look into the search issue...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Turns out the posting Fall Guy was pointing to was moved into the LPC43xx folder of the LPC forum. Its been moved to LPCXpresso IDE now and can be found with a search.

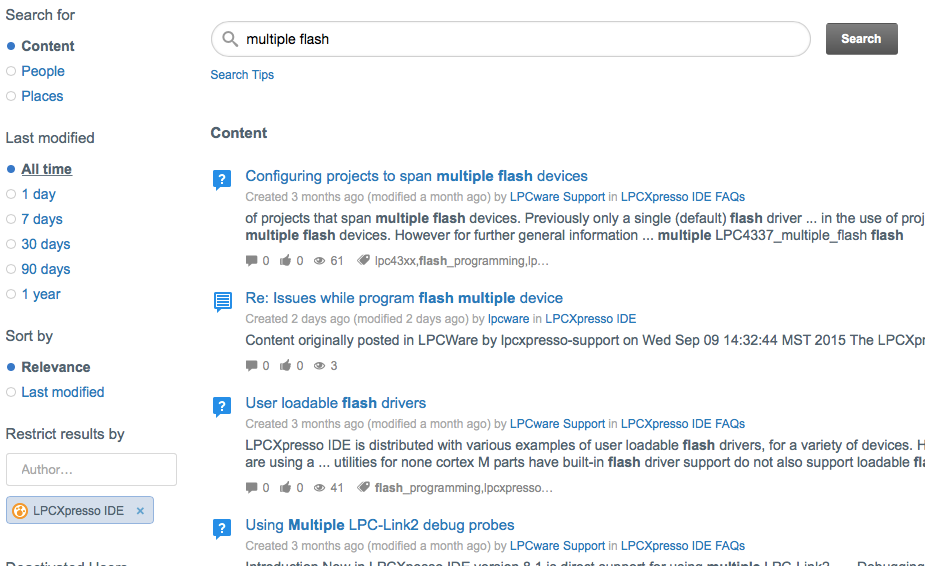

Also, if you search you can remove the (default) limitation to only search the forum you are currently in, thereby including all the forums on the NXP community site. This allows you to search the LPC and LPCXpresso forums at the same time. See the "Restrict results by" section on the bottom left of the screenshot below.