- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- LPCマイクロコントローラ

- :

- eMMC always setting busy bit in cmd1 response

eMMC always setting busy bit in cmd1 response

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi we're using a LPC54608 with an external sandisk (sdinbda6-64g) eMMC memory device which is failing to complete the initialisation phase. (using sdk 2.7.0)

Having looked at the clk, cmd and d0 lines on the scope I can see the processor is sending cmd0 to put it into idle state then is in a constant loop sending cmd1 with the reply always showing bit 31 of OCR as busy (0).

The eMMC part is connected to 3V3 for VCC and VCCQ at 1V8 with power rails measured at 3.32 and 1.81

Is there anything on the nxp processor side that can stop the init phase? Or any extra debug that can be turned on?

Kind regards

Ian

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

To close this off.

In the end we had to change the emmc part to an ISSI one which has now come up first time with no problem.

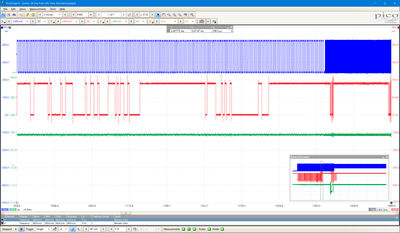

Below is the start up sequence showing the handshaking to up gears through the clock speeds.

The SanDisk part had a line in the hardware design manual that it needed the I/O and core voltage in a sequence outside of the normal jedec spec.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @iann,

What you could do is to modify the MMC_SendOperationCondition to include the MMC_GoIdle that will call the CMD0 again.

Best Regards,

Alexis Andalon

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

To close this off.

In the end we had to change the emmc part to an ISSI one which has now come up first time with no problem.

Below is the start up sequence showing the handshaking to up gears through the clock speeds.

The SanDisk part had a line in the hardware design manual that it needed the I/O and core voltage in a sequence outside of the normal jedec spec.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Alexis,

Thanks for getting back to me, this is on a custom board. A previous prototype board worked with a different eMMC chip from ISSI, that board also had quite different power up characteristics for the Core VCC and the I/O VCCQ which we're currently investigating.

I've looked at the latest sdk changes and can see there's a change to the cmd 1 retries which I've implemented in our version. I was using the mmc example as a test.

Is there a way the sdk driver can be changed to issue another cmd 0 after the cmd 1 number of retries has been reached so it will try again after issuing a reset(cmd0) ?

Cheers

Ian

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @iann ,

Are you using a custom board or a development board? If you're using a custom, could you try replicating this in one of our development boards?

Are you using an SDK example to test this?

Also, the latest SDK available is 2.8.0. so I suggest updating it.

Best Regards,

Alexis Andalon