- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- LPC55xx ADC interrupt routine

LPC55xx ADC interrupt routine

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LPC55xx ADC interrupt routine

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Would I be correct in thinking that the interrupt routine should clear STAT[TCOMP_INT] ?

Without doing so the interrupt routine runs continuously. I don't see any statement to that effect in the manual.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

That was helpful, even 5 years later.

I'm using multiple ADC channels on the LPC55xx. The ADC FIFO is read out when the ADC interrupt fires. I'm using the FIFO watermark interrupt (FWMIE0). Regarding interrupt status bits, I do not have to reset any flags in the ADC status register as they (e.g., RDY0) apparently get reset automatically as soon as the FIFO has been read out completely.

Today I changed the code from FWMIE0 to Trigger completion interrupt ("TCOMP_IE") and my ISR ran continously, as you observed. So to fix this, after reading out FIFO, I have to clear TCOMP_INT bit in the ADC status register by writing a 1 to this bit:

ADC0->STAT &= 1U << ADC_STAT_TCOMP_INT_SHIFT;

I wish NXP would put more effort, time and people to work on the documentation. I'm glad we have this community here.

Thanks

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I figured that the &= operator is probably incorrect. To clear a bit in the ADC status register, you write a 1 to this bit. This should be done using simple assignment:

ADC0->STAT = 1U << ADC_STAT_TCOMP_INT_SHIFT;

Reference: MCUXpresso SDK LPADC_ClearStatusFlags()

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I would suppose any set interrupt flag would cause a continuous interrupt execution. The only difference is, certain flags like result ready get reset automatically on reading the result register.

I use to start out with an interrupt handler that clears all enabled interrupt flags regardless of their status.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

STAT[TCOMP_INT] is for trigger interrupt flag, not ADC result ready interrupt flag.

If you want to use ADC trigger interrupt, yes, you need write 1 to clear it.

About read ADC data interrupt function, please refer to ADC interrupt demo under SDK.

Strongly recommend you debug and run the ADC demo first.

Thanks.

BR

Alice

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

When the SDK creates a project, it creates over 60,000 lines of code. I have searched for ADC0_IRQHandler in most of the logical places it could possibly be, but can't find it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

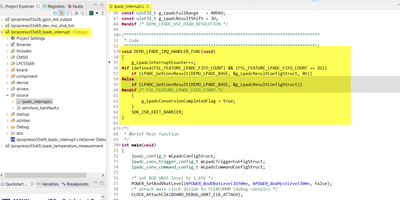

For example lpadc_interrupt demo:

BR

Alice