- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- LPC55S69 CASPER performances detail

LPC55S69 CASPER performances detail

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, In the AN12445 rev. 4, 10/2020, the performances of Figure 8 are illustrated with the columns titles "Flash" and "RAM". I have found no details of what the "Flash" and "RAM" columns mean. Could you please provide an explanation on their difference? Do the SDK allows achieving Flash or RAM performances?

Best regards,

AB

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

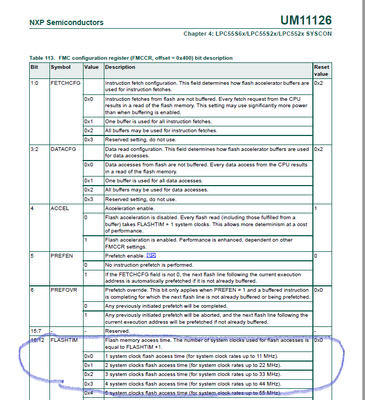

As you know that the LPC55xx has on-chip flash and on-chip RAM, both the on-chip Flash and RAM can be used to save application code and run from them directly. The LPC55S69 for example can run at 150mhz, but reading/executing code from flash requires delay clock, which can be set with the FLASHTIM bits in FMC configuration register. But If you run in on-chip SRAM, delay is not needed, so running in on-chip SRAM is faster than that of running in on-chip flash. user can copy code application code from flash to SRAM and execute in SRAM directly.

For the memory map, pls refer to Chapter 2: LPC55S6x/LPC55S2x/LPC552x Memory Map in UM11126.pdf

Hope it can help you

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you very much for your fast response.

Best regards,

AB

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As you know that the LPC55xx has on-chip flash and on-chip RAM, both the on-chip Flash and RAM can be used to save application code and run from them directly. The LPC55S69 for example can run at 150mhz, but reading/executing code from flash requires delay clock, which can be set with the FLASHTIM bits in FMC configuration register. But If you run in on-chip SRAM, delay is not needed, so running in on-chip SRAM is faster than that of running in on-chip flash. user can copy code application code from flash to SRAM and execute in SRAM directly.

For the memory map, pls refer to Chapter 2: LPC55S6x/LPC55S2x/LPC552x Memory Map in UM11126.pdf

Hope it can help you

BR

XiangJun Rong