- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- Re: LPC5536JBD100 DAC questions

LPC5536JBD100 DAC questions

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LPC5536JBD100 DAC questions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ladies and Gentlemen,

Studying the datasheet and RefManual ( LPC553x Reference Manual, Rev. 3, 07/2023 ) of LPC5536 uC, I have found some hard-to-interpret things.

1.: In the Reference Manual, page 314, table 8.5.1.1.105, there's DAC Isolation Control. I cannot find any more information, what it is? Where is it described, what is DAC isolation?

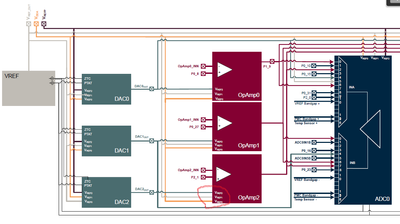

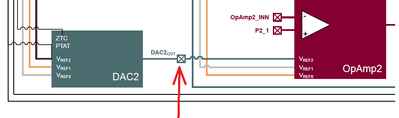

2.: In this device there are 3 DACs. DAC0 and DAC1 are OK, I use them. But: there's DAC2, and it doesn't have any output pin. The only use of this DAC2 I could find is, according to Figure 265, use it as Vref of OpAmp2. But, also on Figure 265, there's an output pin drawn. Also, on Page 93 of Reference Manual, top of page, there's PIO2_4 mentioned as DAC2_OUT. But there's no PIO2_4 pin of this device. My 100 pin package is the highest pin count variant. Did You plan an even higher pin count package for this device?

I have the datasheet, Rev. 5.0 — 7 March 2024, and the Reference Manual, as documentation for this uC. Do I miss any other document?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I appologize for the delay.

Unfortunately, I have not got a clear and official explanation for the DAC isolation feature.

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear XiangJun,

Is there any answer to the "DAC Isolation"? What is that, what does the three DAC_ISO_CTRL bit control? Is there any description of these signals?

LPC553xRM.pdf, page 314, chapter 8.5.1.1.105

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hmm, it is interesting. I got an email from NXP Community, saying, that there's an answer in this topic. But, I don't see any new answer.

My question, Q1, regarding DAC Isolation, is still open.

Q2 is answered, it is clear.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Q1) In the Reference Manual, page 314, table 8.5.1.1.105, there's DAC Isolation Control. I cannot find any more information, what it is? Where is it described, what is DAC isolation?

>>>>>I have asked the AE team for explanation of the " DAC isolation control", will give you a reply after I get response.

Q2)In this device there are 3 DACs. DAC0 and DAC1 are OK, I use them. But: there's DAC2, and it doesn't have any output pin. The only use of this DAC2 I could find is, according to Figure 265, use it as Vref of OpAmp2. But, also on Figure 265, there's an output pin drawn. Also, on Page 93 of Reference Manual, top of page, there's PIO2_4 mentioned as DAC2_OUT. But there's no PIO2_4 pin of this device. My 100 pin package is the highest pin count variant. Did You plan an even higher pin count package for this device?

>>>>>This LPC553x device has three instances of the DAC module, DAC0, DAC1 and DAC2. They are 12 bits resolution. I agree with you that the DAC0 and DAC1 can output the analog voltage to pads, but the DAC2 can not output to a pad. The DAC2 output can be routed to on-chip OP AMP2 and function as a offset voltage for the on-chip OP AMP2.

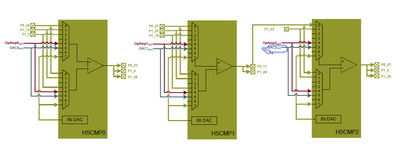

Secondly, the DAC2 can be routed to HSCMP2 as an input channel 5 for both HSCMP non-inverter multiplex and inverter multiplex. The DAC2 is different module from on-chip 8 bits DAC, which is an internal module of the HSCMP.

The PIO2_4 pin does not exist for the current package of LPC553x, so I have suggest AE to delete the pin.

hope it can help you

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hallo Xiangjun,

Thank You for the prompt answer. According to DAC2, Your answer is clear, but there's a symbol in the Reference Manual, Figure 265. At the output of DAC2, there's a little square with cross. In every other case, this symbol means, that the corresponding signal is connected to a pin, to the outside world.

When DAC2 output is an internal signal only, this little square is misleading. Other internal signals, for example OpAmp2 output, they don't have this little square.

Thank You again, I'm waiting the answer regarding DAC Isolation.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

For LPC5536, the DAC2 can not output voltage to an external PAD, so the this is a typo for the little square with cross, I will report it to AE team so that they can modify the doc.

Regarding the "isolation" feature, the question has been escalated to design team, I will reply you after I get feedback.

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank You XiangJun, I am waiting for the next answer.