- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- LPCマイクロコントローラ

- :

- Re: LPC54606 SPI timings?

LPC54606 SPI timings?

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

LPC54606 SPI timings?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

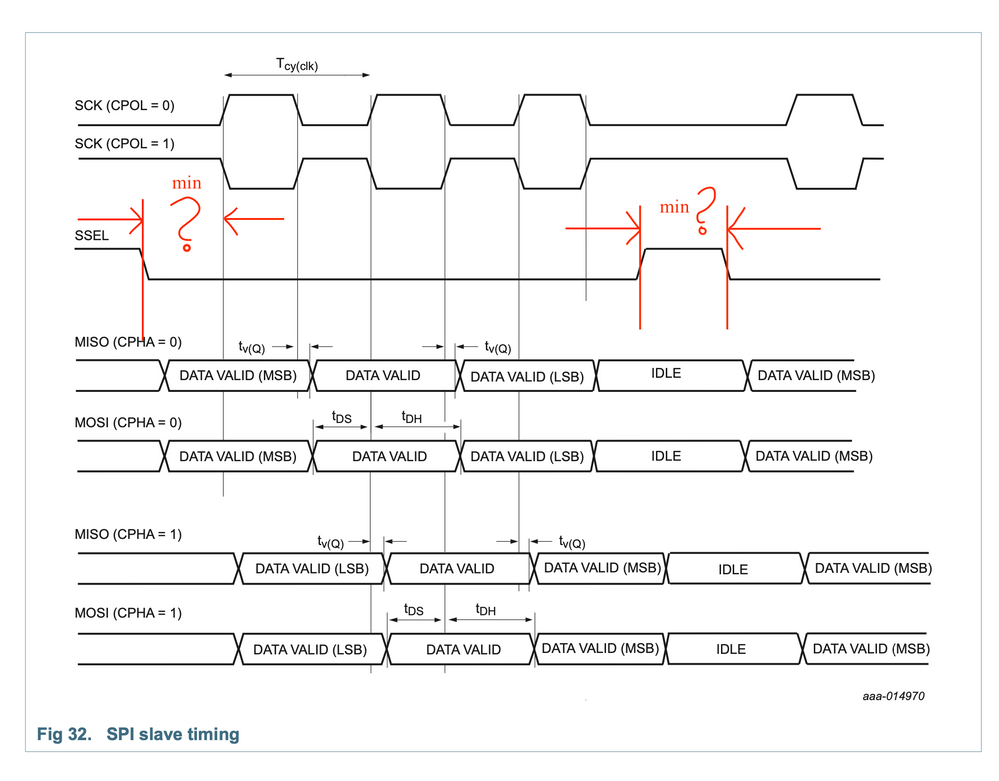

May I know where I can find the actual min & max timings in the SPI read/write timing diagrams? The following image from the user manual does not have the values.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Manu,

The SPI timing spec is defined in data sheet of LPC5460x.pdf, which can be downloaded from the link.

https://www.nxp.com/docs/en/data-sheet/LPC546XX.pdf

If the SPI is configured as master, we have a delay register to define the delay timing. For detailed inf, pls refer to Table 453. SPI Delay register (DLY, offset 0x404) bit description in UM10912.pdf.

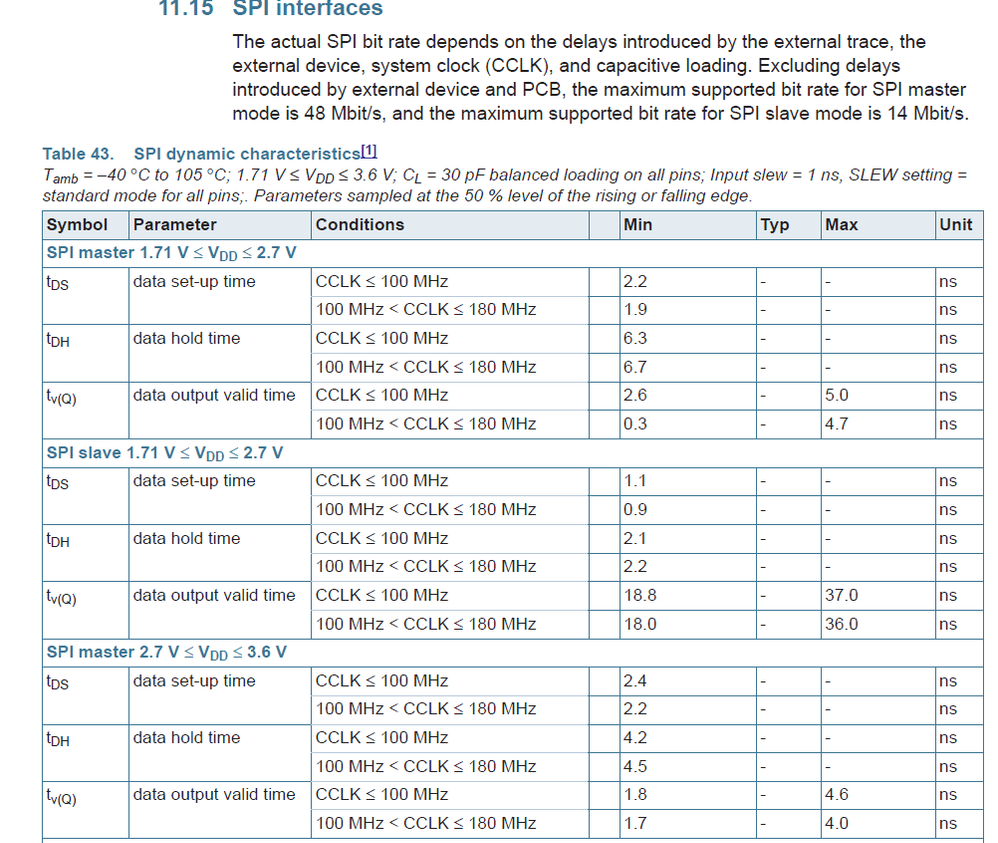

I copy part of it here from data sheet:

Hope it can help you

BR

XiangJun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you for the quick response dear XiangJun Rong.

We are configuring the MCU as an SPI slave (1.71 V ≤ Vdd ≤ 2.7V, CCLK ≤ 100 MHz (FLEXCOMM clock has to be less than 48 MHz from what I understand from the user manual)). I am specifically looking for timings related to the select line (SSEL). Please see the diagram below. If you can share the numbers, that will be extremely helpful for us.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Manu,

Regarding the minimum time between the falling edge of the SSEL signal and the first edge of SCK in CPHA=0, I think the time must meet the tDS(Data set-up time) spec in SPI slave mode. For the minimum high pulse time of the SSEL signal, it is not defined in data sheet.

BR

XiangJun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you for the clarification. Any chance to get the value for "minimum high pulse time of the SSEL signal"? We are connecting our LPC54606 to a device (master) that stream data continuously and so we need to make sure the frame select pulse is long enough that we are within the spec and short enough that we do not lose any data bits.

NOTE: The device doesn't conform to the standard SPI protocol for the SSEL (so we cannot use the device's SSEL) and so we have to generate our own SSEL using an FPGA

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Manu,

Unfortunately, the high pulse time of SSEL for SPI slave of LPC5460x is NOT defined.

BR

XiangJun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you dear XiangJun Rong.