- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- LPCマイクロコントローラ

- :

- Re: Correlation between 2xADC channels at LPC4370

Correlation between 2xADC channels at LPC4370

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Correlation between 2xADC channels at LPC4370

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

we are using LPC4370 and capturing differential signal at 2x ADC channels. MCU is configured for maximum speed - 204MHz. ADc is configured for 80 MHz.

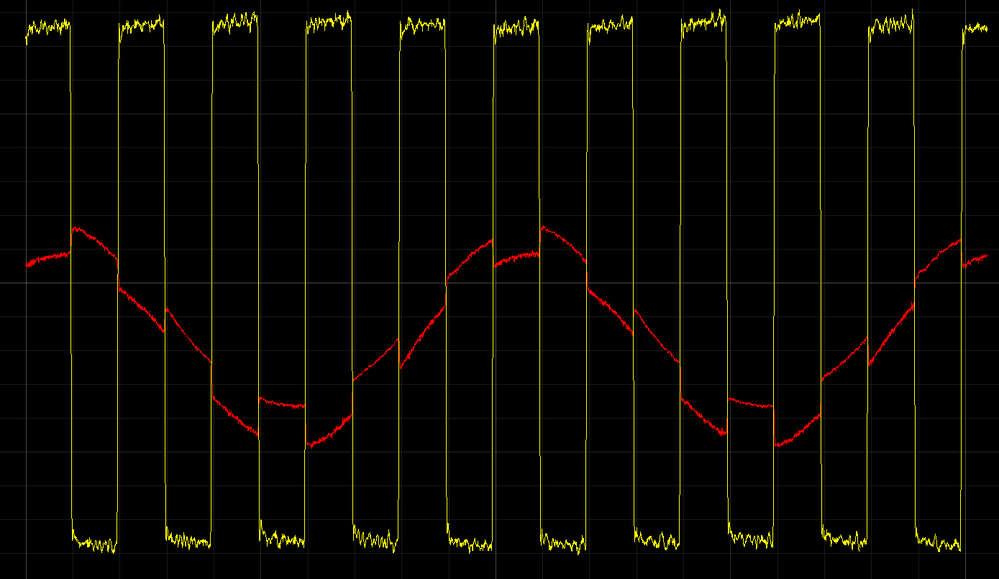

We found, that we have correlation between signals, see picture below:

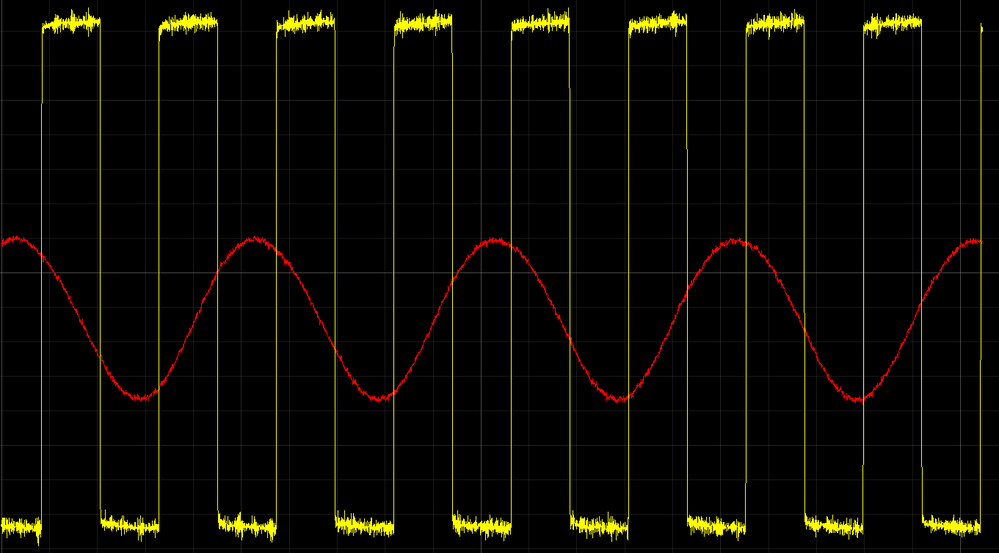

As you can see - that is not an issue of analog front end for sure. We are using DMA, so i dont think that it is an issue with SW. Also we have found, that in case, when ADC is configured for 10MHz - issue is absent:

Does anybody knows, why we have such kind of issue and how to solve it?

We have tried to connect 1k resistor in parallel with ADC input - to discharge ADC - no result.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Sergii,

This is only my guess, as you know that the ADC analog channel is connected to a S/H(sample/hold), which is a capacitor actually. In the sampling phase, the sampling route is connected, the external signal source charges the capacitor of S/H, while the holding route is disconnected. In the Holding phase of S/H component, the sampling route is disconnected, the holding route is connected, the ADC converter samples the voltage of the capacitor of S/H.

I suppose that the your external signal source has not enough driving capacitor, in other words, the external signal source can not provide enough current to charge the capacitor, which leads to the voltage drop. I suggest you use a signal buffer with OP amplifier, for example, connect the tested signal to the non-inverter of OP AMP, connect the inverter pin of AMP to the output pin of AMP, connect the output pin of AMP to ADC analog channel. The AMP output has low impedance and high driving capability.

Pls have a try.

BR

Xiangjun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

we have made our own library, that works OK with 80 MSps. As we can see - that issue is a purely HW issue, due to wrong connection of OPAMP to ADC input. Nothing with SW.

Does anybody have any application notes for this MCU, how to connect OPAMP correctly? What kind of RC network is needed?

--

Regards,

Sergii

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Ok, I would ask if it is possible to have a look, but I bet it's not.

I know nothing about HW set-up, sorry.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Sergii Makovetskyi ,

Sorry I have some confused about the picture, how to get this ? Do you mean ADC result data make up

the curve?

How about the HSADC demo under LPCopen ?

LPCOpen Software for LPC43XX | NXP

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------