- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- 汎用マイクロコントローラ

- :

- LPCマイクロコントローラ・ナレッジ・ベース

- :

- [LPC43xx] LPC43xx series (deep) power down wake-up considerations

[LPC43xx] LPC43xx series (deep) power down wake-up considerations

- RSS フィードを購読する

- 新着としてマーク

- 既読としてマーク

- ブックマーク

- 購読

- 印刷用ページ

- 不適切なコンテンツを報告

[LPC43xx] LPC43xx series (deep) power down wake-up considerations

[LPC43xx] LPC43xx series (deep) power down wake-up considerations

Contents

1.Problem description

2. Reason analysis

3. Solutions

-

3.1 SRAM power down problem solution

3.2 Alarm timer interrupt enable problem solution

3.3 Downcounter register write problem solution

4. Verification Considerations

1. Problem description

When LPC43xx series runs the LPCOpen low-power demo “misc_pmc_states”, the two modes of power down and deep power down cannot successfully wake up through the Alarm Timer. This paper analyzes the series of problems and provides corresponding solutions. The same problem and solution exists for waking up via RTC.

2. Reason analysis

The reasons for wake-up failure include the following three aspects.

- SRAM power down problem: In the power down mode of LPC43xx series, only the 8K SRAM is not powered down, and other SRAMs are powered down. After waking up from power down mode, the program continues to execute backwards, not reset. Therefore, it should be ensured that when entering power down, the data is in the 8K SRAM that does not lose power, so after wake up, it can continue running.

- Alarm timer interrupt enable problem: The LPC43xx Alarm timer interrupt enable need a while to take effect. If it is not successfully enabled before entering low power, it cannot wake up from low power mode.

- Downcounter register problem: In LPC43xx series, in order to ensure the wake-up at the specified time, it is necessary to judge that the set value is successfully written into the Downcounter register.

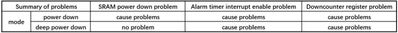

The table of reasons for wake-up failures in power down and deep power down modes is summarized as follows:

3. Solutions

For power down wake-up failure, it needs to be solved according to three problems.

There is no data loss problem for deep power down wakeup. Because after waking up from deep power down mode, the program is reset and executed again, and the previous data is not needed. So the solution skips the first and only needs 3.2 and 3.3.

3.1 SRAM power down problem solution

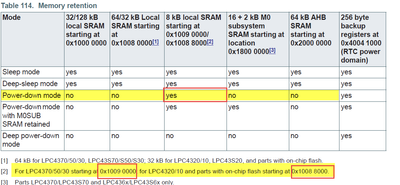

As shown in the manual, only 8kB local SRAM will not lose power in LPC43xx series Power-down mode.

Note: Chips with and without internal flash have different 8K SRAM address ranges.

For LPC4330/LPC4350/LPC4370 series products without internal flash, the 8K SRAM address range is 0x10090000– 0x10092000 (8KB). The address range of chips with internal flash such as LPC4337/LPC4367 is 0x10088000 – 0x1008A000 (8KB).

Placing data in this 8K SRAM area can solve the problem of lost data.

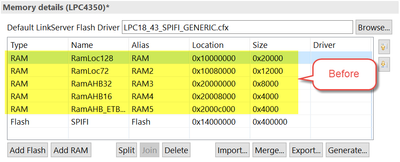

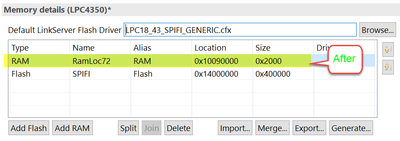

Taking LPC4350 as an example, the setting method in MCUXpressoIDE is as follows:

- Find the following interface according to Project \ Properties \ C\C++ Build\MCU settings path, define this 8K SRAM separately, the address is 0x10090000, and the size is set to 0x2000.

At this point, the setting of the power loss problem in the SRAM area is completed.

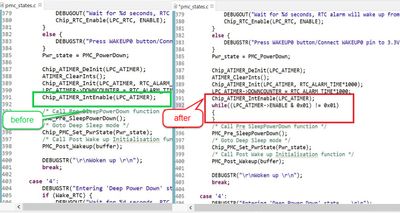

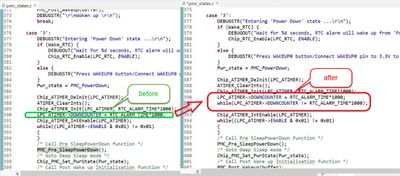

3.2 Alarm timer interrupt enable problem solution

To ensure that the Alarm timer interrupt is enabled, add a while loop poll after it until it is successfully enabled. Enter the function in the src\pmc_states.c path.

And add while((LPC_ATIMER->ENABLE& 0x01) != 0x01){}

after the Chip_ATIMER_IntEnable(LPC_ATIMER); function statement in the corresponding case mode.

3.3 Downcounter register write problem solution

The solution to this problem is similar to 3.2. Still enter the function with the src\pmc_states.c path, and find LPC_ATIMER->DOWNCOUNTER= RTC_ALARM_TIME*1000 in the case of the corresponding mode (consistent with the 3.2 position).

Add a while statement after it:

while(LPC_ATIMER->DOWNCOUNTER != RTC_ALARM_TIME*1000);

As shown below.

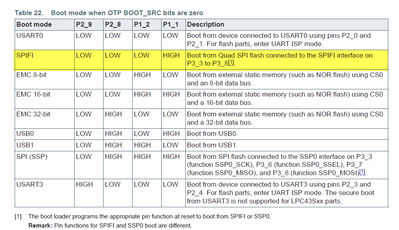

4. Verification Considerations

When there is no internal flash development board for testing (eg: LPC4370, LPC4350…), such as the Hitex LPC4350Evaluation board, it is necessary to configure the startup as external flash startup. The reference picture is as follows.

When starting, you need to set the pins P2_9, P2_8, P1_2, P1-1 to the form of low, low and high, and start in the form of SPIFI. Jumper settings are shown in the figure.