- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers Knowledge Base

- :

- How to use the PLU configuration tool

How to use the PLU configuration tool

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

How to use the PLU configuration tool

How to use the PLU configuration tool

This document is an introduction to how to use the PLU configuration tool.

The PLU programming tool suite that is provided facilitates configuring the PLU to implement the desired logic network. You can download it from the following link:

LPCXpresso804 board for LPC804 Microcontroller (MCU)|NXP

The input to the tool is a Verilog RTL description of the functionality to be implemented. The output of the tool suite provides the following:

1. Values to be programmed into all LUT INPUT MUX registers.

2. Values to be programmed into all LUT TRUTH registers

3. Values to be programmed into all OUTPUT MUX registers

4. Error response if the described network cannot be implemented (most likely due to an excessive amount of logic or use of more than four flip-flops)

5. AC Timing parameters for the implemented design.

PLU tool only connects LUTs to PLU inputs and outputs, users still need to connect PLU inputs, outputs, PLU clk_in to the physical pins via SWM in software.

How to use PLU Config Tool

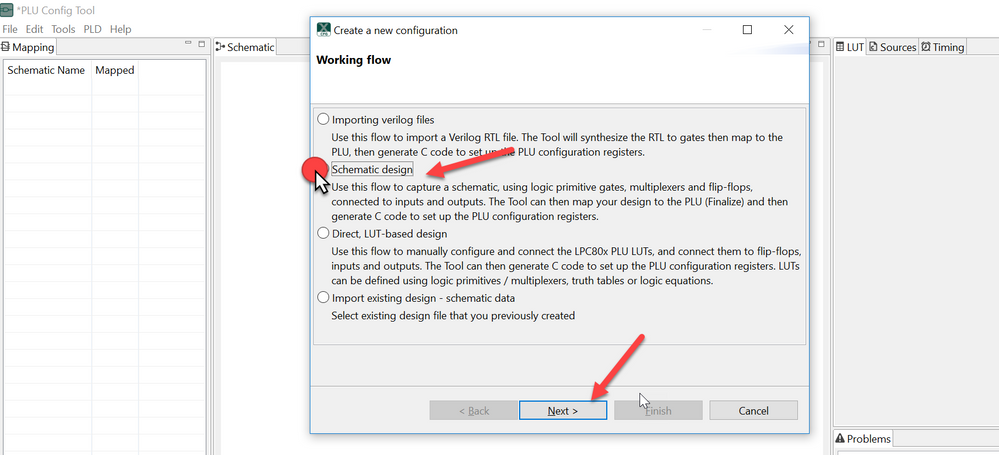

There are 3 ways to design the logic network using the PLU programming tool:

−Import Verilog files

- Use this flow to import a Verilog RTL file. The PLU tool will synthesize the RTL to gates then map to the PLU, then generate C code to set up the PLU configuration registers.

−Schematic design

- Use this flow to capture a schematic, using logic primitives gates, multiplexers and flip-flops, connected to inputs and outputs. The PLU tool can then map your design to the PLU (Finalize) and then generate C code to set up the PLU configuration registers.

−Direct, LUT based design

- Use this flow to manually configure and connect the LPC80x PLU LUTs, and connect them to flip-flops, inputs and outputs. The PLU tool can then generate C code to set up the PLU configuration registers. LUTs can be defined using logic primitives/multiplexers, truth tables or logic equations.

User needs to map the LUTs/gates to the PLU inputs/outputs manually, and finally, PLU tool generates the C code to set up the PLU configuration registers.

Schematic design

This method is very easy to use, the designs are implemented directly using standard gates and muxes. In addition, it is easy to migrate an existing design. The disadvantages are that it is difficult to see exactly how a design is mapped to the LUT hardware (users should do this from register level settings), and it is difficult to implement state machines versus Verilog.

To use this method follow the below steps:

1. Open the PLU tool.

2. Select Schematic Design and click next:

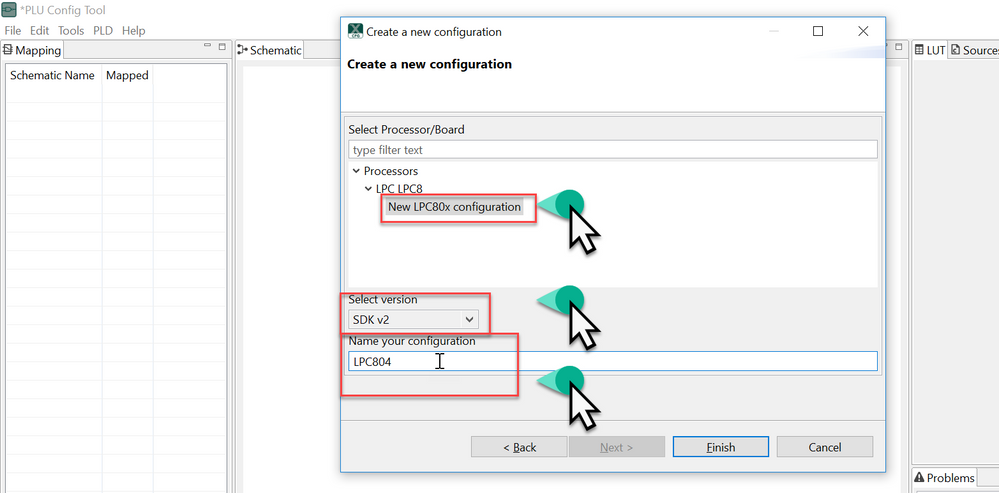

3. Select the processor, SDK version and the name of your configuration then click Finish:

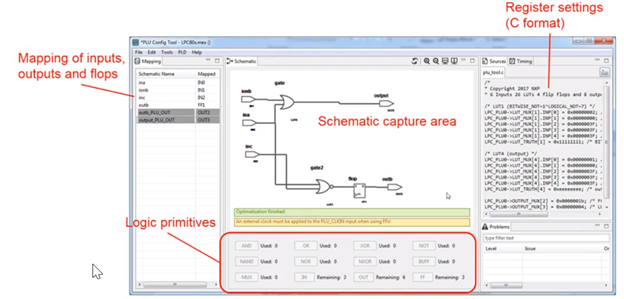

4. At this point, you can start with your design, using the logic gates, multiplexers and flip-flops you can draw your design in the schematic area.

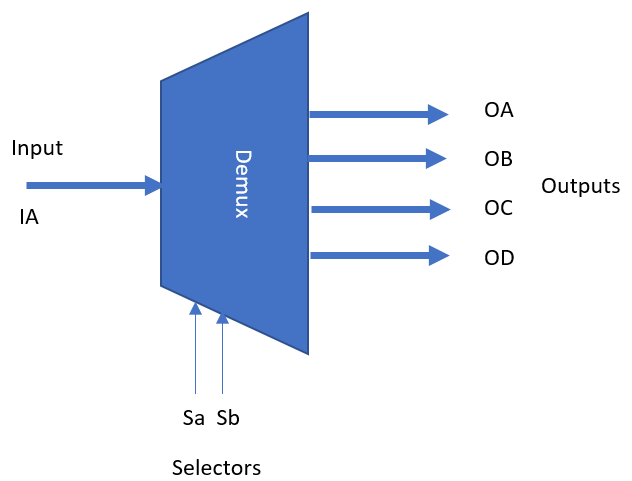

For this example, it is designed a demultiplexer. The demultiplexer takes one single input data line and then switches it to any of the individual output lines one at a time.

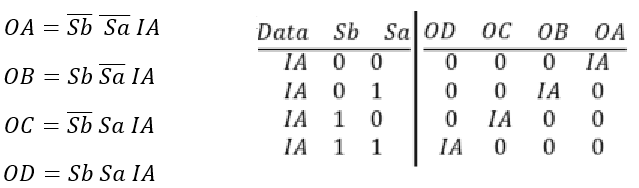

The boolean expressions and true table for the 1-to-4 Demultiplexer shown above with outputs OA to OD and data select lines Sa, Sb are:

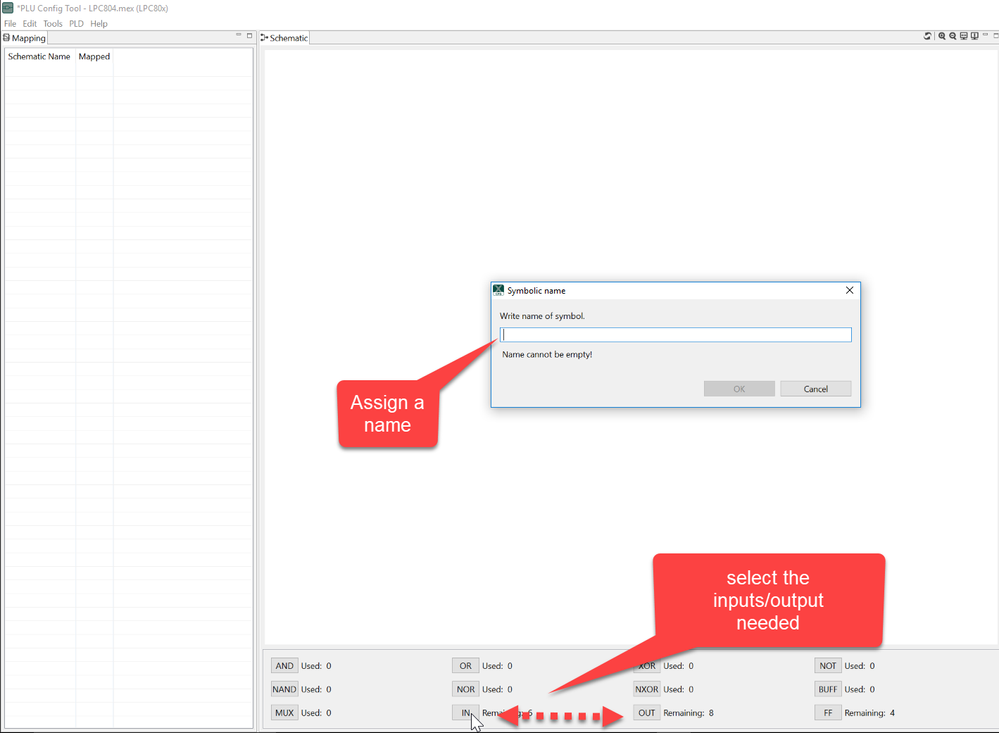

Using the PLU tool, first, select all inputs/output needed and write a name for each of these.

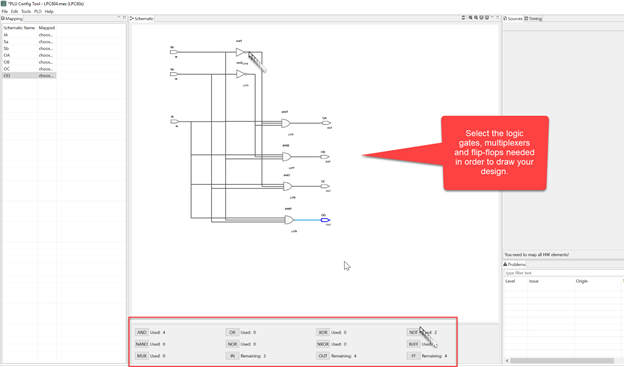

Select the logic gates, multiplexers and flip-flops needed in order to construct your design.

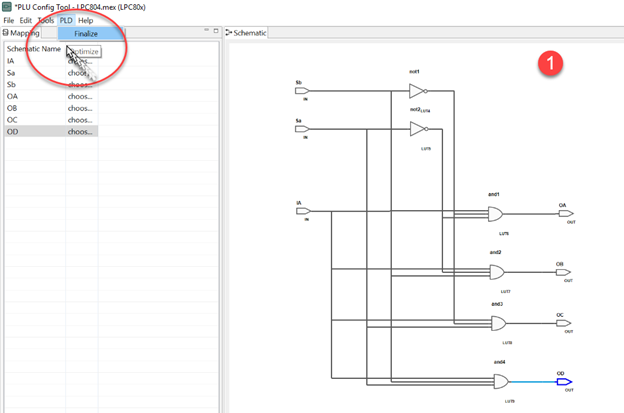

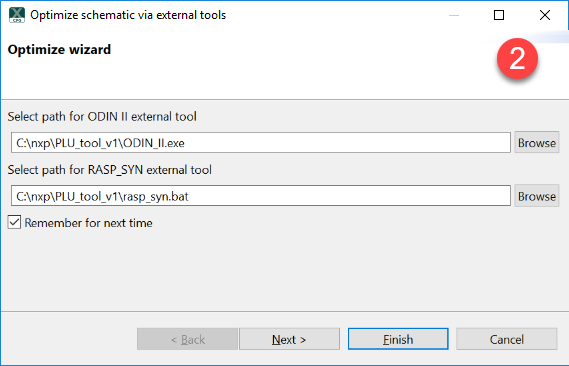

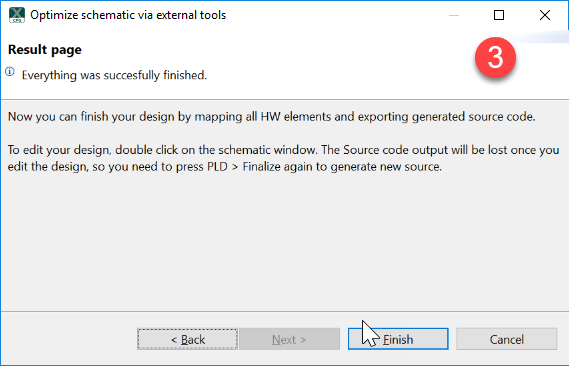

5. After finish your schematic, it is necessary to click on PLD>Finalize, in order to synthesize the design. After this, it will display a new window with information about the location of the external tools used for the optimization. If you click Next, a new window will appear with information regarding the synthesizing process was finalized successfully.

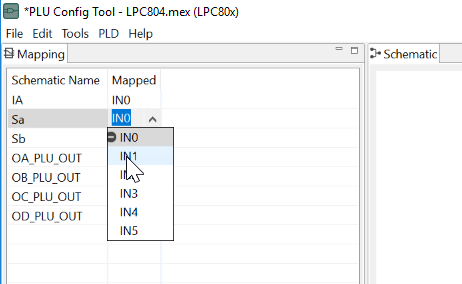

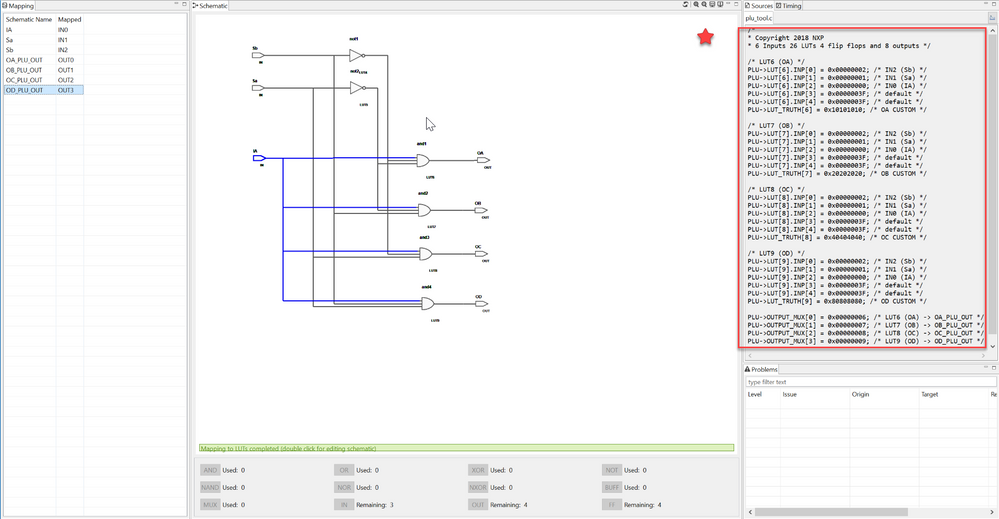

6. In order to generate the C code, it is necessary to map the LUTs/gates to the PLU inputs/outputs manually in the mapping area.

After you specify the connections, the C code will automatically appear in the registers area.

7. Copy and paste the C code into your LPC80x code and remember that the PLU tool only connects LUTs to PLU inputs and outputs, users still need to connect PLU inputs, outputs, PLU clk_in to the physical pins via SWM in software.