- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- MCUXpresso Software and Tools

- :

- Kinetis Software Development Kit

- :

- Re: HELP!!! Last bit of Kinetis DSPI Byte Transfer is Trucated

HELP!!! Last bit of Kinetis DSPI Byte Transfer is Trucated

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Still struggling with trying to get SD Cards working with the K22F and I'm wondering about the dspi clock.

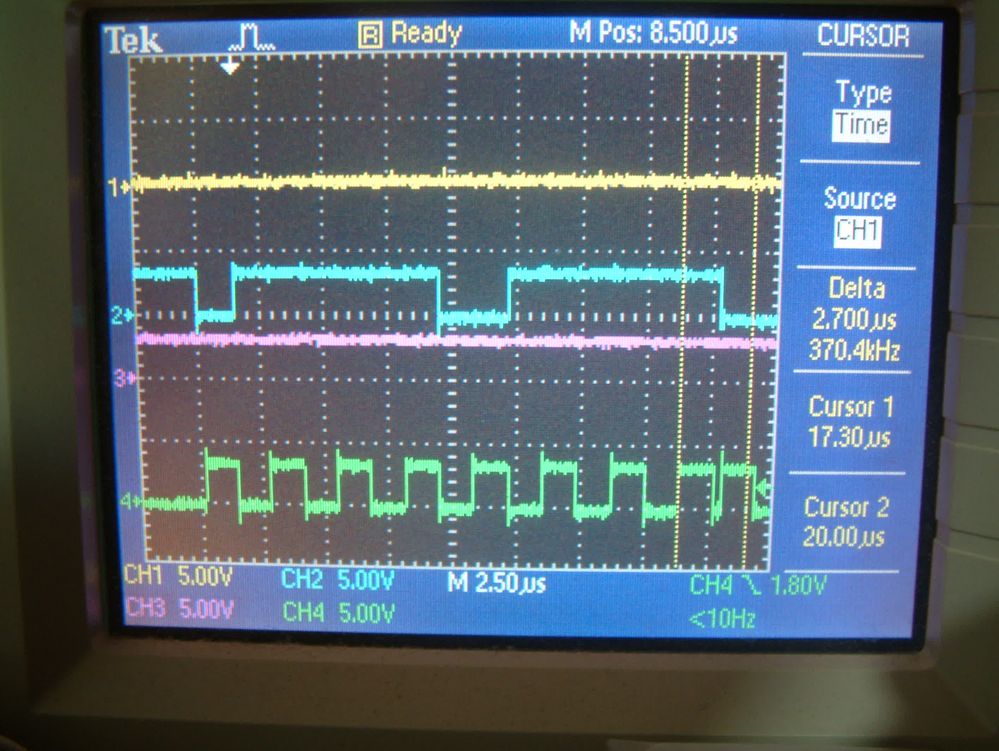

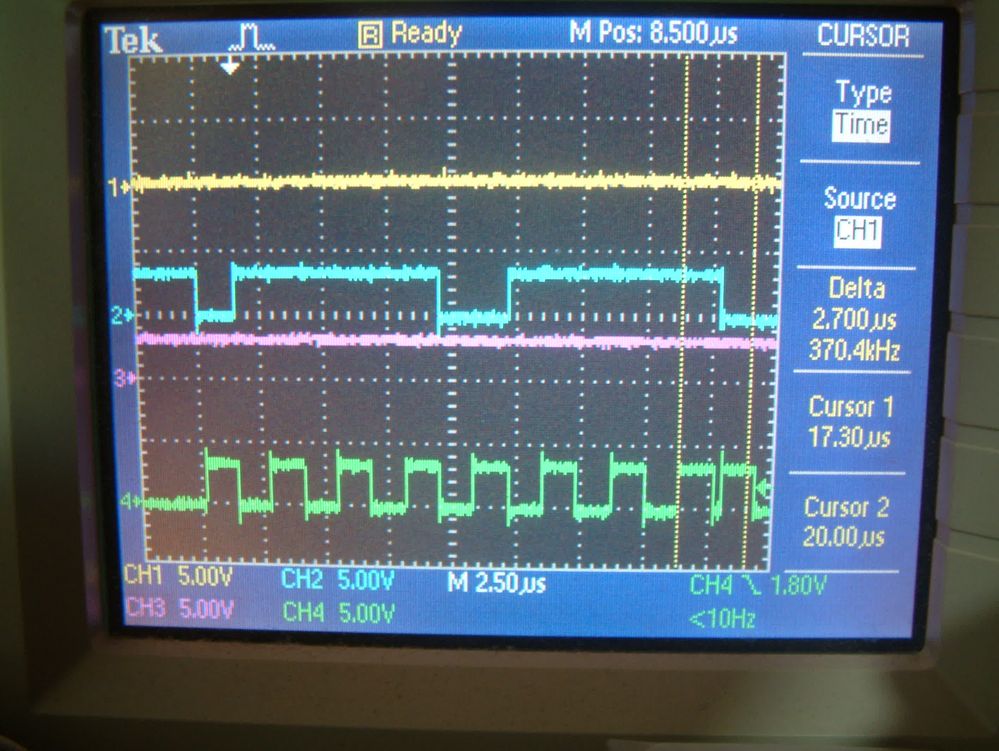

As I mentioned in my previous post, the last bit of a byte transfer is truncated as you can see in this quick and dirty screenshot:

The bottom line is the dspi sck and you can see that the "low" half of the cycle is truncated into the first bit of the next transfer.

The dspi was selected from PE with a clock speed of 375kHz with Clock cfg.4 on a FRDM-k22F board.

I'm looking around and can't find any reason of what I'm doing wrong, 375kHz is a "Possible setting" so I presume that means that the clock is divided evenly (although evidence suggests this is not the case).

Can anybody help?

Thanx,

myke

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

So, I have gotten SD Cards working with the K22F with SPI. I put the code on this https://community.freescale.com/message/612390 thread.

myke

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

So, I have gotten SD Cards working with the K22F with SPI. I put the code on this https://community.freescale.com/message/612390 thread.

myke

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Myke,

I found you posted similar thread in HELP!!! Last bit of Kinetis DSPI Byte Transfer is Trucated , do are they the same issue? is it fixed?

Have a great day,

Kan

NXP Technical Support

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kan,

Yes, it is the same issue and it's fixed with declaring the variable:

uint32_t spi0_ctar0_reg;

and then, after the "DSPI_DRV_MasterConfigureBus" statement, put in:

spi0_ctar0_reg = SPI0_CTAR0 & 0xFF3F0FFF; // Fill out last bit of each byte xfer

spi0_ctar0_reg = spi0_ctar0_reg | 0x00C01000;

SPI0_CTAR0 = spi0_ctar0_reg;

I can obviously simplify the three statements into one without a variable, but this allowed me to observe the progress of the operations.

The values for the changed CTAR0 bits (the PCSSK and CSSK fields in particular) were determined by trial and error (get the GDB plugin that allows you to modify system registers as it will make actions like this a *lot* easier). The K22F's RM was used for information on the CTAR0 register.

Regards,

myke