- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Re: WDOG ist resetting although it is disabled

WDOG ist resetting although it is disabled

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

WDOG ist resetting although it is disabled

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

I'm using a MK10DX64VLH7. Within the project I'm using the watchdog (no window mode) with the LPO as clock source, the timeout value is at 1000ms and the refresh will be every 16ms.

Now I want to disable the watchdog (because I want to set the Controller into sleep mode), so I'm writing a 0 to the WDOGEN Bit.

After that, there will be a while (1) loop (later, I want to set the Controller into vlls3).

Sometimes it happens, that I'm get a WDOG reset..... I can see this in the SRS0 Register.

After some tests, it seems that the WDOG will ignore the disable (WDOGEN = 0). Here is my test application, which will Trigger the WDOG reset very much:

1. refresh the WDOG

2. wait until WDOG->TMROUTL = 1

3. disable the WDOG (WDOGEN = 0, __DSB, __DMB)

4. read the WDOGEN (result = 0)

.... do some other things

5. read the WDOG->TMROUTL (result = 6 or 7)

6. while (1)

7. get the WDOG reset

in this application I'll get the WDOG reset in approximately 9 of 10 tests.

If I'm waiting for WDOG->TMROUTL > 3 (in step 2) everything is fine. In step 5 I'll read 0 - as expected and there will be no reset.

Does anybody know (or have an idea) where could be the problem, that the WDOG is resetting although it will be disabled?

I've read in the Manual (23.7.4 Watchdog Time-out Value Register Low), that there sometimes will be a delay about 4 watchdog clock cycles.....

"The time-out value of the watchdog must be set to a minimum of four watchdog clock

cycles. This is to take into account the delay in new settings taking effect in the watchdog

clock Domain."

Could this be my problem? I thought no, because there is enough time to the WDOGEN = 0 to take effect (~990ms).

If you need any additional information, please let me know.

I'm very thankful for every information or idea, what could cause this behavior.

Best regards,

K-laus

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

If I understand correctly you are using the watchdog for a short time and then trying to disable it.

Remember:

1. The watchdog must be configured within a short time after reset for it to accept the writes

2. If initially used (configuration changed) make sure that the update bit in register CS1 is set - if not it will not be possible to disable it later

3. If you are refreshing the watchdog regularly make your that the refresh sequence is protected from interrupts since an interrupt during the sequece will cause the watchdog to fire

Regards

Mark

Kinetis: µTasker Kinetis support

K60: µTasker Kinetis TWR-K60N512 support / http://www.utasker.com/kinetis/TWR-K60D100M.html / http://www.utasker.com/kinetis/TWR-K60F120M.html

For the complete "out-of-the-box" Kinetis experience and faster time to market

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

thank you very much for your answer.

The "AllowUpdate-Bit" is set and the interrupts are disabled while refreshing.

I still wonder, why the WDG counter is counting although the WDG is disabled.

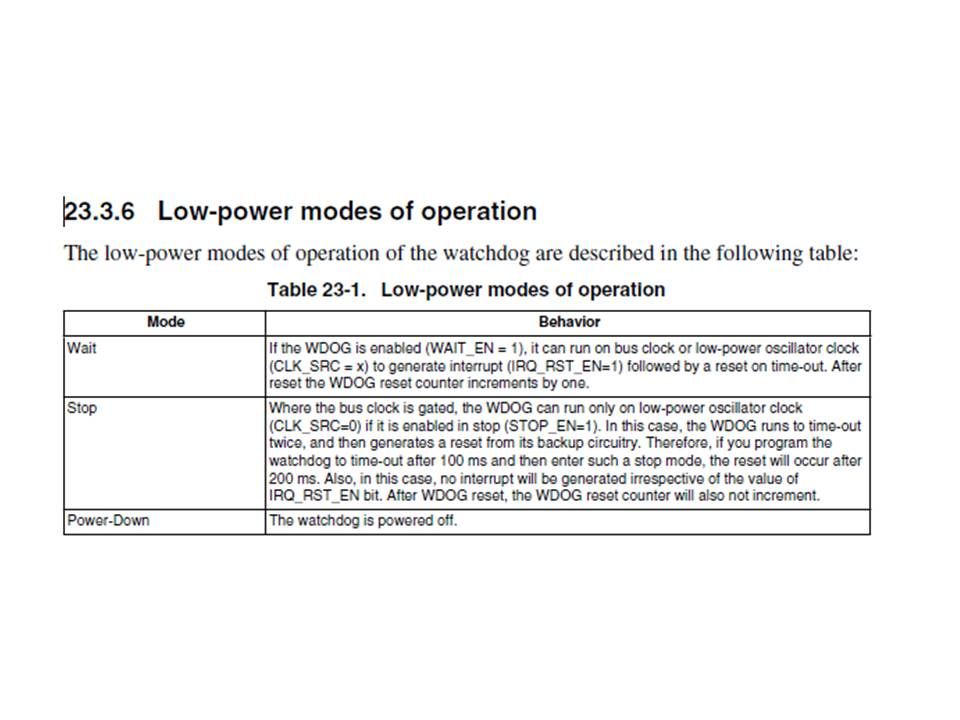

23.3.5 Watchdog disabled mode of operation

When the watchdog is disabled through the WDOG_EN bit in the watchdog status and

control register, the watchdog timer is reset to zero and is disabled from counting until

you enable it or it is enabled again by the system reset

When I disable the WDG while the WDG counter is 1, the WDG is still counting. If I wait for the WDG counter becomes 4 and then disable the WDG, everything is fine. It's possible that the WDG ignores the disable, when it's written while the WDG counter is 1? In the manual sometimes is written about 3 clock cycles, which the WDG needs to synchronize itself....

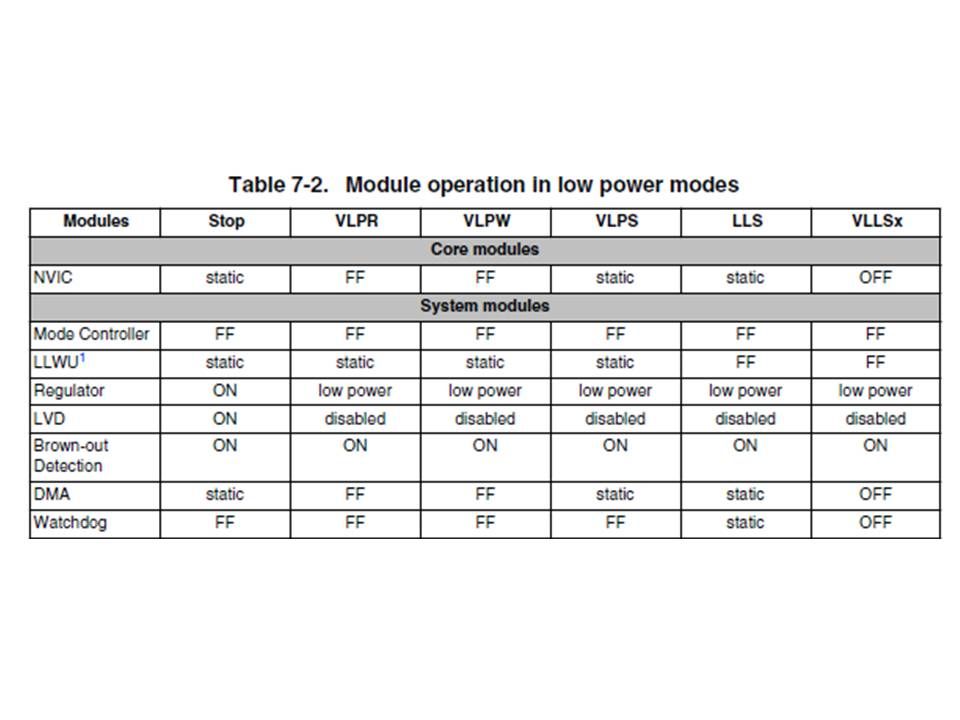

Now I've implemented the VLLS3 after disable the WDG. I still get the WDG resets.... I'm a little bit confused because of this two comments in the manual:

Here the WDG should be powered off in VLLS3.

And here it still will be working in VLLS3. - If I understand correctly (the STOP_EN is set). I'm using the LPO.

When I've a look at my behavior, it looks like the Stop description in 23.3.6.

I can read the WDG as the reset source in the SRS register, but the WDG reset counter doesn't increase....

Now I've tested it with STOP_EN not set, but I get the same behavior....

Do you have any other ideas, what do I have to do to disable the WDG definitely?

I can't wait for the WDG is counting till 4 every time....

Best regards,

K-laus

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

I have always done the following (with almost all K parts) to perminently disable the watchdog and never had any any issues with it:

UNLOCK_WDOG(); // open a window to write to watchdog

WDOG_STCTRLH = (WDOG_STCTRLH_STNDBYEN | WDOG_STCTRLH_WAITEN | WDOG_STCTRLH_STOPEN | WDOG_STCTRLH_CLKSRC); // disable watchdog

If I have previously had the watchdog running (before disabling it) I would have used:

UNLOCK_WDOG(); // open a window to write to watchdog

WDOG_TOVALL = (2000/5);

WDOG_TOVALH = 0;

WDOG_STCTRLH = (WDOG_STCTRLH_ALLOWUPDATE | WDOG_STCTRLH_STNDBYEN | WDOG_STCTRLH_WAITEN | WDOG_STCTRLH_STOPEN | WDOG_STCTRLH_WDOGEN); // watchdog enabled to generate reset on 2s timeout (allow updates later if required)

Regards

Mark

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

you are right - this works (nearly in all cases) in my application too.

But I have the problem, that it sometimes doesn't work. So I've tried, what do I have to do to reproduce that the watchdog is resetting although it is disabled.

-> I have to disable the WDOG, when the WDOG_TMROUTL = 1

This is also the reason, why it only happens sometimes -> It happens, when I've disabled the WDOG just after refreshing it. And then never refresh the WDOG again (Go into while(1) or VLLS3).

Do you also have tried to disable the WDOG while WDOG_TMROUTL = 1 and then never refresh it?

I've to stop my application asynchronously to the WDOG-refresh. So it would be fine, to be able to disable the WDOG all the time definitely.

Best regards,

K-laus

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello K dannenmann:

I think you are running into similar situation as discussed in this thread: WDOG ignoring refresh when using LPO clock

It's a long discussion but the bottom line is that you need to wait for those 4 WDOG clock cycles, in this case 4 LPO cycles after refreshing the WDOG to disable it. If you cannot wait so long then consider using the bus clock for the watchdog.

Regards!

Jorge Gonzalez

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Jorge Gonzales,

yes, you are right.... It seems to be a similar situation/behavior.... thank you for the hint....

So I have two options at the moment... wait 4 clock cycles or use the bus clock....

I have had some hope, that somebody could say this behavior is due to.... (exactly reason)... so that I can really understand the behavior....

Now it seems to be working, but I'm not sure, if it works all the time....

Thank you very much for your help Mark Butcher and Jorge Gonzales.

Best regards,

K-laus