- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- 通用微控制器

- :

- Kinetis微控制器

- :

- Update pwm duty cycle at rising edge

Update pwm duty cycle at rising edge

Update pwm duty cycle at rising edge

Hello,

I have a problem with the settings of my pwm (K27). I'm updating the duty-cycle periodically. But even if the old and new duty cycle are the same, I see a jitter on my scope. Here, the "high" phase of the output signal is longer than it should be (e.g. 22us inset of 13us). So it seems that the couter is always started during a "high" phase. Is there any possibility to adopt the new duty cycle at a rising edge? I've tried several combinations of SWRSTCNT, SYNCMODE a.s.o, but did not find the correct combination.

Do you have any ideas?

Have you refer the methods in ftm example of MCUXpresso SDK_2.5.0_MK27FN2M0Axxx15?

Try to find examples that are similar to what you need then test.

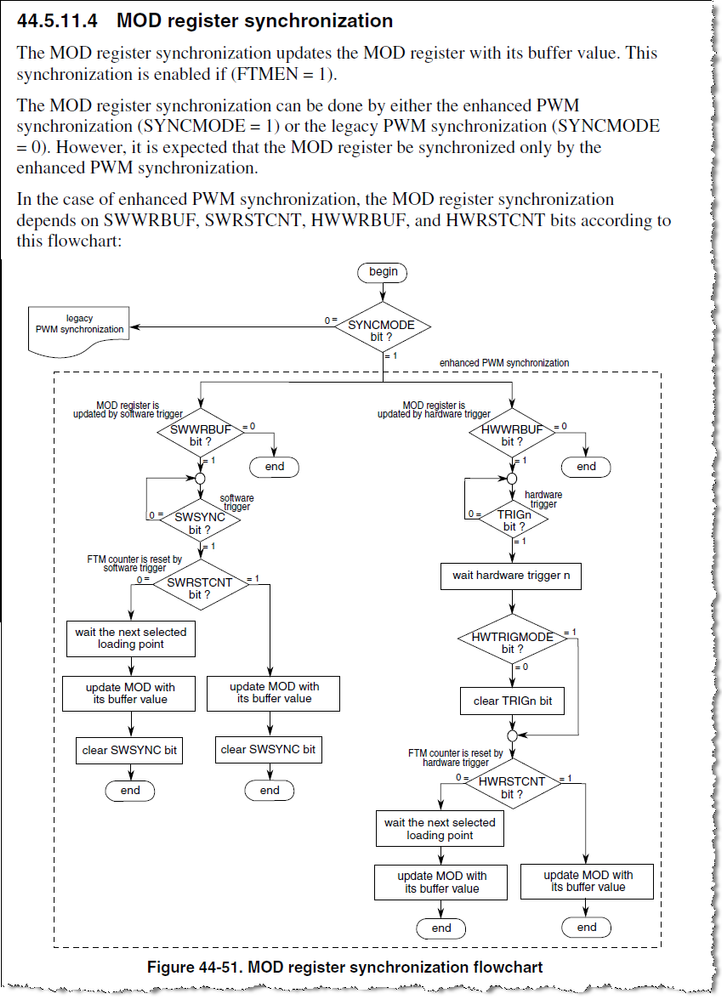

For more detail, please read the "44.5.11.4 MOD register synchronization".

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

----------------------------------------------------------------------------------------------------------------------