- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- TWR-KW24D512 MCG FEI mode

TWR-KW24D512 MCG FEI mode

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

TWR-KW24D512 MCG FEI mode

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I am now using TWR-KW24D512 and wants to keep TWR-KW24D512 running under MCG FEI mode after reseting.

I did not change the default register value for MCG_C1 and MCG_C4, and also use the factory's trim value after resetting.

Could I confirm that the board is running under FEI mode?

Could I know what is the rate of the system clock? Is it 32.768kHz?

Could I know UART module clock is the system clock?

I encounter a UART issue after resetting. The UART does not work properly if the UART module clock is 32768*640.

But it begins to work, if the UART module clock is 32768*480....

Could I know the reason?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Lu,

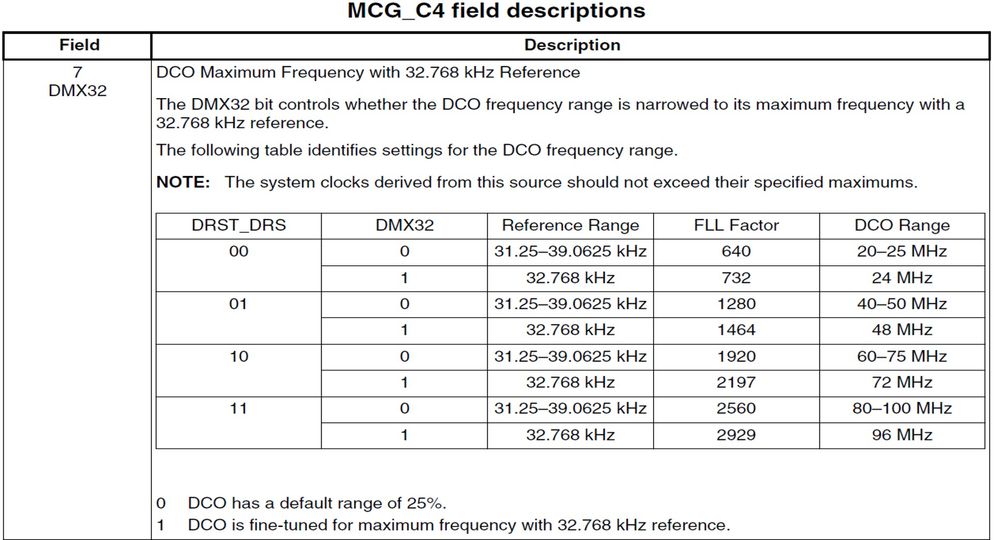

In MCG_C4 register, you can look at default FLL Factor for your MCU (DRST_DRS and DMX32 fields), by default, the FLL factor is 640 so DCO Range is between 20-25 MHz, also notice that there is not lower frequency than 20 MHz for DCO.

Other thing that you can do is to check Slow Internal Reference Clock Fine Trim settings (SCFTRIM field on MCG_C4 register) in both boards, maybe the trimming value is not the same in both board and that is why MCGOUTCLK frequency is different in both boards.

Hope this helps,

Regards,

Isaac

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Lu Wang,

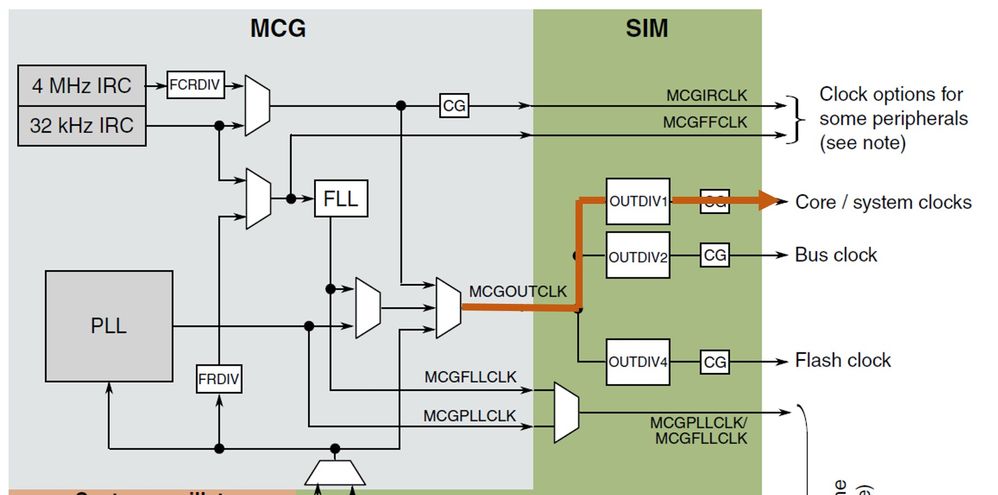

After Reset, FEI mode is configured by default, in this mode, MCGOUTCLK clock is taken from FLL that is internally using the Slow Internal Reference clock (32 kHz) and multiplication factor of 640, so, MCGOUTCLK clock is 20.97 MHz.

Basically, to corroborate that MCU is configured in FEI mode, you need to validate that:

- MCG_S[CLKST] field is 0x00 (It means that FLL is selected)

- MCG_S[IREFST] field is 1 (It means that FLL reference clock is the internal reference clock)

- MCG_S[PLLST] filed is 0 (it means that FLL output is used instead of PLL)

If these conditions are accomplished, then, you are working on FEI mode.

About UART clocking, in section 12.7.7 UART clocking from Reference Manual, it says that UART0 and UART1 operate from core/system clock and all other UART modules opera from Bus clock.

Remember that core/system clock is taken from MCGOUTCLK / OUTDIV1 value, that is set in SIM_CLKDIV1 register:

So, if OUTDIV1 is set to 0, then Core\System clock is equal to MCGOUTCLK / 1 = MCGOUTCLK. (20.97MHz at reset).

About the issue you are facing, just validate that FLL is using default values so Core clock is set to 20.97MHz and under this value, calculate SBR and BRFD values.

I hope this can help you!

Best Regards,

Isaac Avila

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Isaac,

Thanks for your support!

I checked the following register values:

MCG_S[CLKST] = 0

MCG_S[IREFST] = 1

MCG_S[PLLST] = 0

OUTDIV1 = 0

SBR and BRFD calculation is exactly the same as code in the bsp package (bsp/PLM/Source/Uart/UART.c).

But UART still does not work, if the platform clock is set as 20.97MHz after reset.

Are there any other registers that I need to check?

I have two boards, one is marked as year 2013, the other is marked as 2014.

The board marked with 2013 works properly with the code.

But the board marked with 2014 does not work, unless I change the platform clock when calculating SBR and BRFD.

Can you give me any explanations?

Lu

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Lu,

What application are you using? and what revision are your boards?

Regards,

Isaac

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I am using the application built by ourselves.

It is really simple: initialize GPIO, enable UART clock, configure UART registers (115200 8N1).

If system clock is 32768*640 to calculate SBR and BRFD, the UART always get messy code.

But I system clock is around 15MHz, the UART works with few bit errors.

I attached the photos of the board I used.

NXP Community <https://community.freescale.com/resources/statics/1000/35400-NXP-Community-Email-banner-600x75.jpg>

TWR-KW24D512 MCG FEI mode

reply from isaacavila <https://community.freescale.com/people/isaacavila?et=watches.email.thread> in Kinetis Microcontrollers - View the full discussion <https://community.freescale.com/message/625399?et=watches.email.thread#comment-625399>

Hello Lu,

What application are you using? and what revision are your boards?

Regards,

Isaac

Reply to this message by replying to this email, or go to the message on NXP Community <https://community.freescale.com/message/625399?et=watches.email.thread#comment-625399>

Start a new discussion in Kinetis Microcontrollers by email <mailto:discussions-community-kinetis@mail.freescale.jiveon.com> or at NXP Community <https://community.freescale.com/choose-container.jspa?contentType=1&containerType=14&container=2019&et=watches.email.thread>

Following TWR-KW24D512 MCG FEI mode <https://community.freescale.com/message/625399?et=watches.email.thread#comment-625399> in these streams: Inbox

This email was sent by NXP Community because you are a registered user.

You may unsubscribe <https://community.freescale.com/unsubscribe.jspa?email=luwan%40nestlabs.com&token=a70b4ac9c0f9352eb2efb3284f3ab9cfd25ae6965a1a173d2fef803e1629a804> instantly from NXP Community, or adjust email frequency in your email preferences <https://community.freescale.com/user-preferences!input.jspa>