- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: Stuck with LPSPI (MKE14F)

Stuck with LPSPI (MKE14F)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Forum,

i just want to send out plain data over SPI, it can't be too hard, right?

However, I'm stuck with it, maybe you guys can help me out.

Code:

void lpspi_init(void){

//configure port

PCC->CLKCFG[PCC_PORTD_INDEX]=PCC_CLKCFG_CGC(1);

PORTD->PCR[0]=PORT_PCR_MUX(3);

PORTD->PCR[1]=PORT_PCR_MUX(3);

PORTD->PCR[2]=PORT_PCR_MUX(3);

PORTD->PCR[3]=PORT_PCR_MUX(3);

//Set FIRCDIV2

SCG->FIRCDIV=SCG_FIRCDIV_FIRCDIV2(1)|SCG_FIRCDIV_FIRCDIV1(1);

//configure

PCC->CLKCFG[PCC_LPSPI1_INDEX]=PCC_CLKCFG_CGC(1)|PCC_CLKCFG_PCS(3); //Set fast irc clock

//Reset module

// Reset all internal logic and registers, except the Control Register. Remains set until cleared by software.

LPSPI1->CR |= LPSPI_CR_RST_MASK;

// Software reset doesn't reset the CR, so manual reset the FIFOs

LPSPI1->CR |= LPSPI_CR_RRF_MASK | LPSPI_CR_RTF_MASK;

// Master logic is not reset and module is disabled.

LPSPI1->CR = 0x00U;

//Set SPI to master mdoe

LPSPI1->CFGR0=LPSPI_CFGR0_HRSEL(1); //does not work with 0 too.

LPSPI1->CFGR1=LPSPI_CFGR1_MASTER(1);

LPSPI1->TCR=LPSPI_TCR_PRESCALE(1)|LPSPI_TCR_PCS(1)|LPSPI_TCR_FRAMESZ(8);

LPSPI1->CCR= 0x04090808;

LPSPI1->FCR=0x00000003;

LPSPI1->CR=LPSPI_CR_MEN(1);

}

I'm not getting any output on the pins. Where's my problem?

I then write test data to it:

LPSPI1->TDR=0b01010101;

However I do not see anythings on the pins.

1. Is my clock right? Fast IRC is running on 48MHz.

Can somebody please assit me to get the code running?

-Michael

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Following is my hand written code that works. In case anybody has the same problem.

void lpspi0_init(void){

//Configure pins

CLOCK_EnableClock(kCLOCK_PortD);

PORTD->PCR[0]=PORT_PCR_MUX(3)|PORT_PCR_DSE(1);

PORTD->PCR[1]=PORT_PCR_MUX(3)|PORT_PCR_PE(1)|PORT_PCR_PS(1);

PORTD->PCR[2]=PORT_PCR_MUX(3)|PORT_PCR_DSE(1);

PORTD->PCR[3]=PORT_PCR_MUX(3)|PORT_PCR_DSE(1);

CLOCK_EnableClock(kCLOCK_Lpspi1);

CLOCK_SetIpSrc(kCLOCK_Lpspi1, kCLOCK_IpSrcSysPllAsync);

LPSPI1->CR=0;

LPSPI1->IER=0;

LPSPI1->DER=0;

LPSPI1->CFGR0=0;

LPSPI1->CFGR1=LPSPI_CFGR1_MASTER(1)|LPSPI_CFGR1_SAMPLE(1); //Master mode

LPSPI1->TCR=LPSPI_TCR_CPOL(0)|

LPSPI_TCR_PRESCALE(4)|

LPSPI_TCR_PCS(0)|

LPSPI_TCR_LSBF(0)|

LPSPI_TCR_BYSW(0)|

LPSPI_TCR_CONT(0)|LPSPI_TCR_CONTC(0)|

LPSPI_TCR_RXMSK(0)|

LPSPI_TCR_TXMSK(0)|

LPSPI_TCR_WIDTH(0)|

LPSPI_TCR_FRAMESZ(15);

LPSPI1->CCR= LPSPI_CCR_SCKPCS(10)|

LPSPI_CCR_PCSSCK(0)|

LPSPI_CCR_DBT(16);

LPSPI1->FCR=LPSPI_FCR_RXWATER(0)|

LPSPI_FCR_TXWATER(3);

LPSPI1->CR= LPSPI_CR_DBGEN(1)|LPSPI_CR_MEN(1);

//DMA STUFF

LPSPI1->DER|=LPSPI_DER_RDDE(1)|LPSPI_DER_TDDE(1); //Enable recieve dma request

ADS7947_DMA_lpspi1_rx();

//Flush FIFO

LPSPI1->CR |= (1<< LPSPI_CR_RTF_SHIFT) | (1<< LPSPI_CR_RRF_SHIFT);

//Clear SR

LPSPI1->SR = 0xFFFFFFFF;

LPSPI1->TCR =

(LPSPI1->TCR & ~(LPSPI_TCR_CONT_MASK | LPSPI_TCR_CONTC_MASK | LPSPI_TCR_RXMSK_MASK | LPSPI_TCR_PCS_MASK)) |

LPSPI_TCR_CONT(0) | LPSPI_TCR_CONTC(0) | LPSPI_TCR_RXMSK(0) | LPSPI_TCR_PCS(0);

ADS7947_DMA_SPI_tx();

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

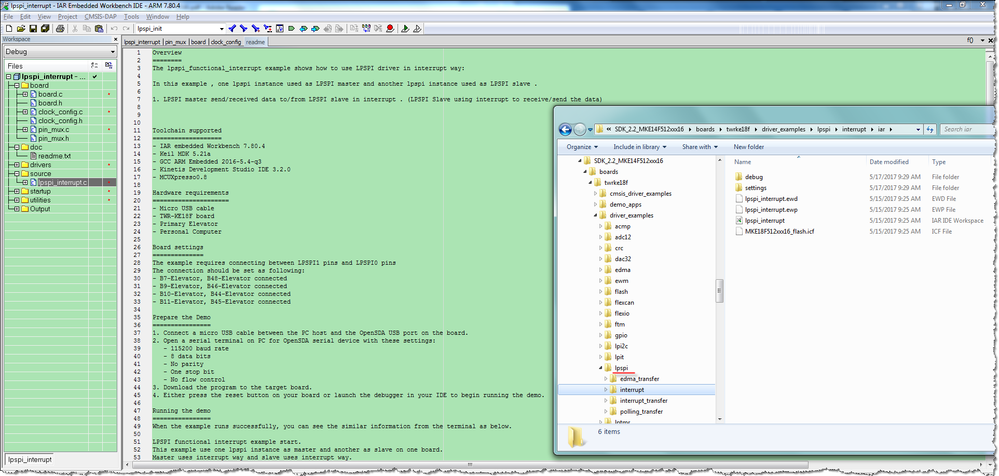

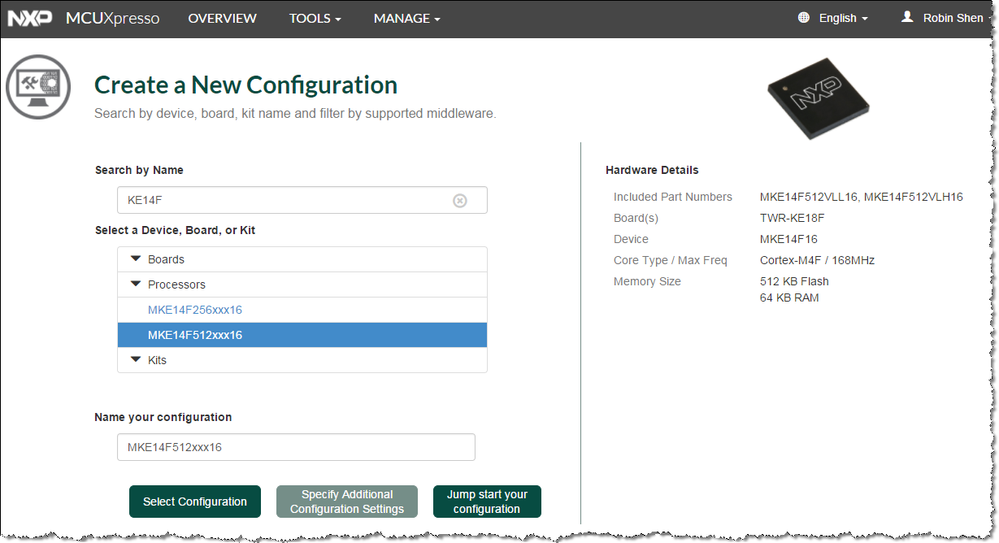

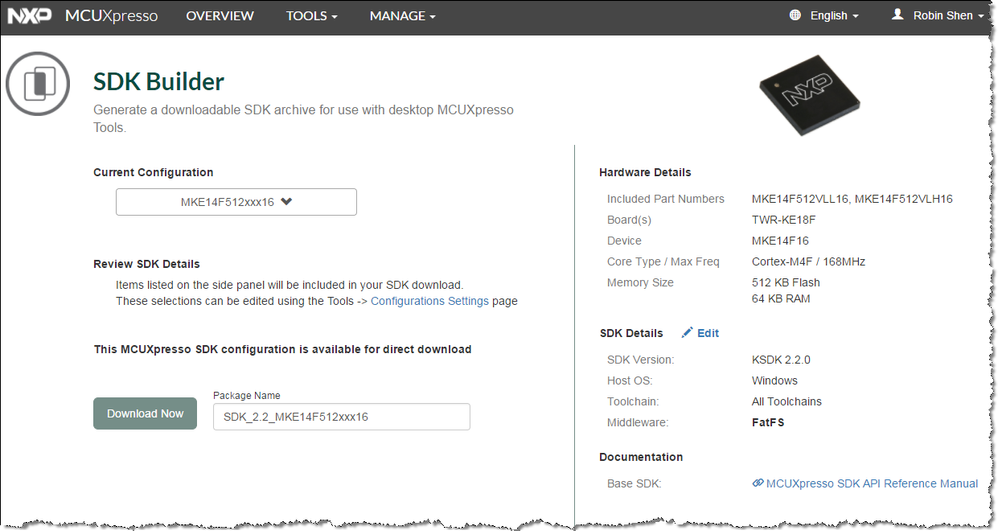

Have you try to test the LPSPI demo in SDK_2.2_MKE14F512xxx16?

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, i had a look at the example, however I could not find the problem.

I found the cookbook (page 38) to get a sample code.

http://www.nxp.com/assets/documents/data/en/application-notes/AN5413.pdf

I implemented the code 1to1 and it did not solve my problem for one week now:

void lpspi_cookbook(void){

//configure port

PCC->CLKCFG[PCC_PORTD_INDEX]=PCC_CLKCFG_CGC(1);

PORTD->PCR[0]=PORT_PCR_MUX(3);

PORTD->PCR[1]=PORT_PCR_MUX(3);

PORTD->PCR[2]=PORT_PCR_MUX(3);

PORTD->PCR[3]=PORT_PCR_MUX(3);

//Set FIRCDIV2

//SCG->FIRCDIV=SCG_FIRCDIV_FIRCDIV2(1)|SCG_FIRCDIV_FIRCDIV1(1);

//configure

PCC->CLKCFG[PCC_LPSPI1_INDEX]=0;

PCC->CLKCFG[PCC_LPSPI1_INDEX]=PCC_CLKCFG_CGC(1)|PCC_CLKCFG_PCS(3); //Set fast irc clock

CLOCK_SetIpSrc(kCLOCK_Lpspi1, kCLOCK_IpSrcFircAsync);

LPSPI1->CR=0;

LPSPI1->IER=0;

LPSPI1->DER=0;

LPSPI1->CFGR0=0;

LPSPI1->CFGR1=LPSPI_CFGR1_MASTER(1); //Master mode

LPSPI1->TCR=LPSPI_TCR_CPOL(0)|

LPSPI_TCR_PRESCALE(0)|

LPSPI_TCR_PCS(0)|

LPSPI_TCR_LSBF(0)|

LPSPI_TCR_BYSW(0)|

LPSPI_TCR_CONT(0)|LPSPI_TCR_CONTC(0)|

LPSPI_TCR_RXMSK(0)|

LPSPI_TCR_TXMSK(0)|

LPSPI_TCR_WIDTH(0)|

LPSPI_TCR_FRAMESZ(15);

LPSPI1->CCR= LPSPI_CCR_SCKPCS(0)|

LPSPI_CCR_PCSSCK(1)|

LPSPI_CCR_DBT(8);

LPSPI1->FCR=LPSPI_FCR_RXWATER(0)|

LPSPI_FCR_TXWATER(3);

LPSPI1->CR= LPSPI_CR_DBGEN(1)|LPSPI_CR_MEN(1);

}

i verified that i have 48MHZ at the FIRC.

Fits perfectly.

void verfiy_clock(void){

//page 26

PCC->CLKCFG[PCC_PORTE_INDEX]=PCC_CLKCFG_CGC(1);

SIM->CHIPCTL=SIM_CHIPCTL_CLKOUTSEL(1);

SCG->CLKOUTCNFG=SCG_CLKOUTCNFG_CLKOUTSEL(3);

PORTE->PCR[10]=PORT_PCR_MUX(2) | PORT_PCR_DSE(1);

}

However, it seems to me, honestly, that now clock arrives. I configured the clocks right.

const scg_sys_clk_config_t g_sysClkConfig_BOARD_BootClockRUN =

{

.divSlow = kSCG_SysClkDivBy5, /* Slow Clock Divider: divided by 5 */

.divBus = kSCG_SysClkDivBy2, /* Bus Clock Divider: divided by 2 */

.divCore = kSCG_SysClkDivBy1, /* Core Clock Divider: divided by 1 */

.src = kSCG_SysClkSrcSysPll, /* System PLL is selected as System Clock Source */

};

const scg_sosc_config_t g_scgSysOscConfig_BOARD_BootClockRUN =

{

.freq = 0U, /* System Oscillator frequency: 0Hz */

.enableMode = kSCG_SysOscEnable | kSCG_SysOscEnableErClk,/* Enable System OSC clock, Enable OSCERCLK */

.monitorMode = kSCG_SysOscMonitorDisable, /* Monitor disabled */

.div1 = kSCG_AsyncClkDivBy2, /* System OSC Clock Divider 1: divided by 2 */

.div2 = kSCG_AsyncClkDivBy1, /* System OSC Clock Divider 2: divided by 1 */

.workMode = kSCG_SysOscModeExt, /* Use external clock */

};

const scg_sirc_config_t g_scgSircConfig_BOARD_BootClockRUN =

{

.enableMode = kSCG_SircEnable | kSCG_SircEnableInLowPower,/* Enable SIRC clock, Enable SIRC in low power mode */

.div1 = kSCG_AsyncClkDisable, /* Slow IRC Clock Divider 1: Clock output is disabled */

.div2 = kSCG_AsyncClkDisable, /* Slow IRC Clock Divider 2: Clock output is disabled */

.range = kSCG_SircRangeHigh, /* Slow IRC high range clock (8 MHz) */

};

const scg_firc_config_t g_scgFircConfig_BOARD_BootClockRUN =

{

.enableMode = kSCG_FircEnable, /* Enable FIRC clock */

.div1 = kSCG_AsyncClkDivBy1, /* Fast IRC Clock Divider 1: divided by 1 */

.div2 = kSCG_AsyncClkDivBy1, /* Fast IRC Clock Divider 2: divided by 1 */

.range = kSCG_FircRange48M, /* Fast IRC is trimmed to 48MHz */

.trimConfig = NULL, /* Fast IRC Trim disabled */

};

const scg_spll_config_t g_scgSysPllConfig_BOARD_BootClockRUN =

{

.enableMode = kSCG_SysPllEnable, /* Enable SPLL clock */

.monitorMode = kSCG_SysPllMonitorDisable, /* Monitor disabled */

.div1 = kSCG_AsyncClkDisable, /* System PLL Clock Divider 1: Clock output is disabled */

.div2 = kSCG_AsyncClkDivBy1, /* System PLL Clock Divider 2: divided by 1 */

.src = kSCG_SysPllSrcFirc, /* System PLL clock source is Fast IRC */

.prediv = 3, /* Divided by 4 */

.mult = 4, /* Multiply Factor is 20 */

};

/*******************************************************************************

* Code for BOARD_BootClockRUN configuration

******************************************************************************/

void BOARD_BootClockRUN(void)

{

scg_sys_clk_config_t curConfig;

/* Init FIRC. */

CLOCK_CONFIG_FircSafeConfig(&g_scgFircConfig_BOARD_BootClockRUN);

/* Init SIRC. */

CLOCK_InitSirc(&g_scgSircConfig_BOARD_BootClockRUN);

/* Init SysPll. */

CLOCK_InitSysPll(&g_scgSysPllConfig_BOARD_BootClockRUN);

/* Set SCG to SPLL mode. */

CLOCK_SetRunModeSysClkConfig(&g_sysClkConfig_BOARD_BootClockRUN);

/* Wait for clock source switch finished. */

do

{

CLOCK_GetCurSysClkConfig(&curConfig);

} while (curConfig.src != g_sysClkConfig_BOARD_BootClockRUN.src);

/* Set SystemCoreClock variable. */

SystemCoreClock = BOARD_BOOTCLOCKRUN_CORE_CLOCK;

/* Set PCC LPSPI1 selection */

CLOCK_SetIpSrc(kCLOCK_Lpspi1, kCLOCK_IpSrcFircAsync);

/* Set PCC LPUART1 selection */

CLOCK_SetIpSrc(kCLOCK_Lpuart1, kCLOCK_IpSrcSysPllAsync);

}

It seems to me that the clock gets somehow lost on the way. I can send some data, with the following function, but then the transmission stop as fifo is full.

void LPSPI1_transmit_16bits(uint16_t send) {

while((LPSPI1->SR & LPSPI_SR_TDF_MASK)>>LPSPI_SR_TDF_SHIFT==0);

LPSPI1->TDR = send;

LPSPI1->SR |= LPSPI_SR_TDF_MASK;

}

Any help is highly apprechiated. I spend on this now one week and feel really stupid.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Following is my hand written code that works. In case anybody has the same problem.

void lpspi0_init(void){

//Configure pins

CLOCK_EnableClock(kCLOCK_PortD);

PORTD->PCR[0]=PORT_PCR_MUX(3)|PORT_PCR_DSE(1);

PORTD->PCR[1]=PORT_PCR_MUX(3)|PORT_PCR_PE(1)|PORT_PCR_PS(1);

PORTD->PCR[2]=PORT_PCR_MUX(3)|PORT_PCR_DSE(1);

PORTD->PCR[3]=PORT_PCR_MUX(3)|PORT_PCR_DSE(1);

CLOCK_EnableClock(kCLOCK_Lpspi1);

CLOCK_SetIpSrc(kCLOCK_Lpspi1, kCLOCK_IpSrcSysPllAsync);

LPSPI1->CR=0;

LPSPI1->IER=0;

LPSPI1->DER=0;

LPSPI1->CFGR0=0;

LPSPI1->CFGR1=LPSPI_CFGR1_MASTER(1)|LPSPI_CFGR1_SAMPLE(1); //Master mode

LPSPI1->TCR=LPSPI_TCR_CPOL(0)|

LPSPI_TCR_PRESCALE(4)|

LPSPI_TCR_PCS(0)|

LPSPI_TCR_LSBF(0)|

LPSPI_TCR_BYSW(0)|

LPSPI_TCR_CONT(0)|LPSPI_TCR_CONTC(0)|

LPSPI_TCR_RXMSK(0)|

LPSPI_TCR_TXMSK(0)|

LPSPI_TCR_WIDTH(0)|

LPSPI_TCR_FRAMESZ(15);

LPSPI1->CCR= LPSPI_CCR_SCKPCS(10)|

LPSPI_CCR_PCSSCK(0)|

LPSPI_CCR_DBT(16);

LPSPI1->FCR=LPSPI_FCR_RXWATER(0)|

LPSPI_FCR_TXWATER(3);

LPSPI1->CR= LPSPI_CR_DBGEN(1)|LPSPI_CR_MEN(1);

//DMA STUFF

LPSPI1->DER|=LPSPI_DER_RDDE(1)|LPSPI_DER_TDDE(1); //Enable recieve dma request

ADS7947_DMA_lpspi1_rx();

//Flush FIFO

LPSPI1->CR |= (1<< LPSPI_CR_RTF_SHIFT) | (1<< LPSPI_CR_RRF_SHIFT);

//Clear SR

LPSPI1->SR = 0xFFFFFFFF;

LPSPI1->TCR =

(LPSPI1->TCR & ~(LPSPI_TCR_CONT_MASK | LPSPI_TCR_CONTC_MASK | LPSPI_TCR_RXMSK_MASK | LPSPI_TCR_PCS_MASK)) |

LPSPI_TCR_CONT(0) | LPSPI_TCR_CONTC(0) | LPSPI_TCR_RXMSK(0) | LPSPI_TCR_PCS(0);

ADS7947_DMA_SPI_tx();

}