- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: KV46F PWM misbehavior when connecting FreeMaster or setting break-point

KV46F PWM misbehavior when connecting FreeMaster or setting break-point

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

KV46F PWM misbehavior when connecting FreeMaster or setting break-point

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am having an issue with the KV46F256 microcontroller when connecting to it via FreeMASTER using BDM communication plugin OR also when just setting a break-point at a part of the code that is not being executed while the code is running.

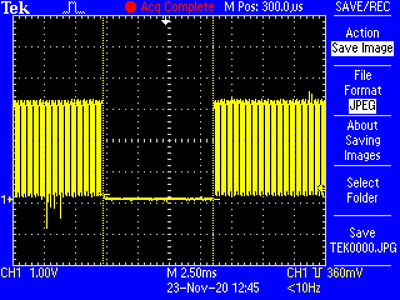

I noticed that my motor was doing a noise every time I set a break-point or any time I try to connect via FreeMaster. Looking the PWM signals for my phase U upper switch I found the following:

There is an interruption of the PWM signals for about 8.8 milliseconds then it resumes to normal operation. I really believe this should NOT be happening specially when connecting with FreeMaster as this can cause damage to bigger motors.

Is there a way to stop this interruption of the PWMs when connecting to the micro via FreeMaster and/or setting a break-point?

I am using the latest version of SDK for the KV46F256 micro, I am using the MCUXpresso IDE v11.2.0 [Build 4120] [2020-07-09] and my debug probe is the Multilink Universal FX.

Sincerely,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Please note that when you are connecting over JTAG/BDM plug-in, you should abort the debugging session first. The P&E Micro probe must NOT be occupied by a debugger when connecting with FreeMASTER. If you need to debug while running Freemaster then I recommend you to connect over serial line as you can have both debugger and FreeMASTER running.

I believe this is the reason why you are seeing unexpected behavior when placing a breakpoint.

Best regards,

Felipe

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm NOT trying to connect FreeMASTER while debugging. I described two scenarios where the problem occurs:

First scenario: When debugging and I add/remove a breakpoint at a piece of code not being executed.

Second scenario: When not debugging and I connect to the micro via FreeMaster using the BDM plugin.

Both scenarios stop the PWM switching for about 8.8mS which I believe to not be the correct behavior as I'm performing non-intrusive operations.

Sincerely,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I've received feedback from Freemaster team.

Just to confirm - I hope the glitch on PWM signal is only observed when FreeMASTER is just establishing connection...? It should NOT be observed during normal communication - that would be really bad.

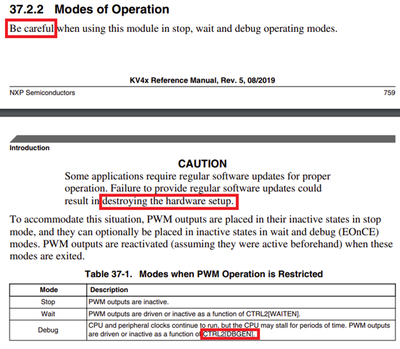

When FreeMASTER is connecting (and also when a debugger communicates with target while setting a breakpoint etc), the JTAG temporarily forces the CPU to a background/suspended mode to analyze the connection. I think it is normal/default behavior that the peripheral clocks are suspended during this period - causing the PWM glitch. The KV4x reference manual writes about it in section 37.2.2. It may indeed be dangerous to the motor hardware.

The customer should consider setting the CTRL2[DBGEN] bit in PWM configuration.

Hope it helps!

Best regards,

Felipe

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored. Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Felipe,

The problem with that approach is:

My PWM will not stop anymore but the duty cycle will be kept constant (because CPU isn't running to recalculate the new PWMs) for the same amount of time which translate to applying DC voltage to the motor (high currents are produced).

So, it seems like this is a glitch that can cause issues no matter what.

Do you know if this is something that NXP/ARM is planning to fix in a soon-to-come future?

Sincerely,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Unfortunately, there is no plan to fix this issue yet. I am sorry for the inconvenience that this may have caused you.

Best regards,

Felipe

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Felipe,

I don't know if you really understand how big of a problem this is. I'm unable to debug my code when my hardware is connected to a motor. I cannot even set a breakpoint because doing so will either stop my PWMs for some milliseconds causing issues (since all my lowers go enabled and it short my motor) or keep my PWMs running without an updated duty cycle which is even more catastrophic for the hardware.

I should not experience this type of issues when just setting breakpoints on my code (notice that I'm not really stopping the code execution, I'm just setting breakpoints). I've used other types of motor control micros such as TI C2000 and have never experienced this type of behavior.

I really would like to get a better evaluation of this issue other than just apologies.

Sincerely,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for the clarification. I have contacted Freemaster team to see whether this is expected behavior or not. I will update this thread as soon as I receive more information.

Best regards,

Felipe