- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Re: KL26Z 5V Tolerant Inputs

KL26Z 5V Tolerant Inputs

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

KL26Z 5V Tolerant Inputs

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

“The Kinetis Port pins are only 5V tolerant as inputs. The outputs are not 5V tolerant, and that includes pins configured as open-drain outputs. In output mode, if the pin is pulled above VDD, it will cause the output buffer to drive the output at VDD, which will pull-down the pin voltage to near VDD.”

I ran across this comment in a previous thread.

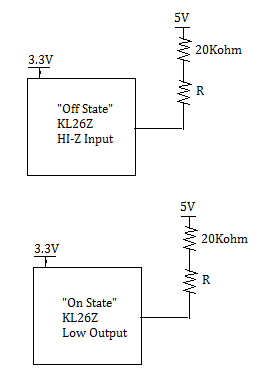

I want to configure a GPIO on the KL26Z we are using as a Hi-Z input (no internal pull up or down) that is externally pulled up to 5V through >20Kohm resistors and then to simulate button presses by turning that GPIO to a low output then back to a Hi-Z input. From the previous comment it seems that this is reasonable if the pins are 5V tolerant as inputs. I wanted to confirm this, or find where I am mistaken.

Also, I have scoured KL26 datasheets for the technical data that would support this if confirmed and can’t find any references. Is this documented somewhere?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Tarik,

But there is no words say KL26 is 5v tolerant. The max input voltage is 3.6V. Please don't connect 5v signal.

Regards,

Jing

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

In the thread posted above it mentions if the GPIO is configured as an input for Kinetis series it would be 5V tolerant. I have this working with no damage on the freedom board for the KL26Z. I see that for the K64 and other in the kinetis series denotes 5V tolerant inputs in datasheets, is the KL26Z different?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

No, not all kinetis have 5v tolerant pin.

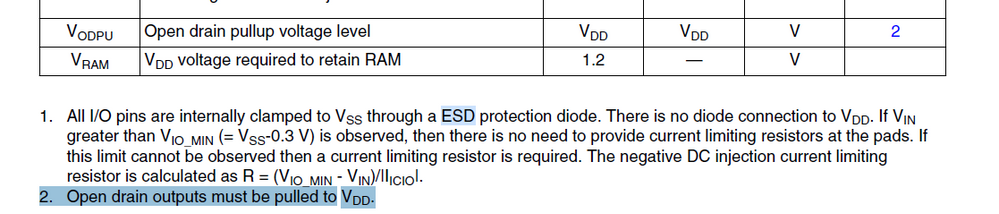

This is table 5 in KL26 datasheet.

Yes, I agree pullup through a 20k resistor to 5V can protect the pin. The current is very small. Since there isn't ESD to VDD, there isn't current to VDD also.

Regards,

Jing

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I understand it is not recommended. I just want to know if it will cause damage. In the "Off State" as an input with the external resistor there should be little current to damage the chip. In the "On State" the GPIO is configured as a low output. I don't think either state would damage the chip. I just want to see if I am overlooking something.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I think it's fine.

Regards,

Jing