- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: KL17 FlexIO - Shift Neg Clock Edge - No Shift takes place

KL17 FlexIO - Shift Neg Clock Edge - No Shift takes place

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

KL17 FlexIO - Shift Neg Clock Edge - No Shift takes place

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The FlexIO is pretty straight forward -- that's why this is perplexing me.

FlexIO described her and in KL reference manual: https://community.nxp.com/docs/DOC-105640

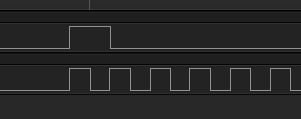

Here is the data and clock output from a FlexIO data and clock channel. -- I'm only showing the first data bit because I'm interested on what edge the data shift out.

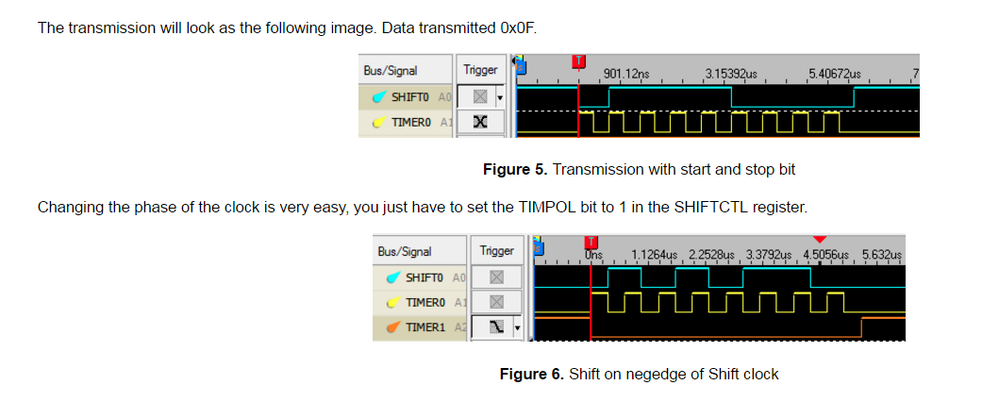

Here is a similar image from the reference post above.

In both cases, the data is shifting out on the rising (positive) clock edge.

I want my data to shift on the falling (negative) clock edge.

As noted in the 2nd image above, all one SHOULD have to do is to change the Shifter Control TIMPOL value from 0 (shift positive edge) to 1 (shift negative edge) ... as shown in second pic above.

When I set TIMPOL to shift on falling edge -- the complete shift operation STOPS!! NO data comes out the shifter pin.

I return TIMPOL back to 0 and all shifting operations work -- "on rising clock edge"

Can someone please comment on what the issue may be?

Thanks.

Joe

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Xiangjun:

Any update on your findings?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Xiangjun:

Thanks for looking into this.

Here is the core flexio code: http://joehinkle.com/DownLoad/HinklePixelPWR.zip

I set up an IO channel (both shifter and clock pins exposed) with this call. It produces the waveform with clocking on positive clock edge I posted earlier.

Shift channel = 0

Timer channel = 0

Shifter pin = 0

timer pin = 1

clock at 800khz

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you post your code here so that we can review and debug your code on our FRDM board?

BR

Xiangjun Rong