- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Re: K70 External DDR2 RAM Debugging

K70 External DDR2 RAM Debugging

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Currently I'm using IAR IDE to do the debugging.

I'm using the macro file K70_MT47H64M16HR-3.mac from bare metal and the icf is something like below:

define symbol __ICFEDIT_intvec_start__ = 0x70000000;

/*-Memory Regions-*/

define symbol __ICFEDIT_region_ROM_start__ = 0x70000000;

define symbol __ICFEDIT_region_ROM_end__ = 0x7007FFFF;

define symbol __ICFEDIT_region_RAM_start__ = 0x20000000;

define symbol __ICFEDIT_region_RAM_end__ = 0x2000FFF0;

/*-Sizes-*/

define symbol __ICFEDIT_size_cstack__ = 0x00;

define symbol __ICFEDIT_size_heap__ = 0;

/**** End of ICF editor section. ###ICF###*/

define exported symbol __EXTERNAL_MRAM_ROM_BASE = 0x10000000;

define exported symbol __EXTERNAL_MRAM_ROM_SIZE = 0x00060000;

define exported symbol __EXTERNAL_MRAM_RAM_BASE = 0x10060000;

define exported symbol __EXTERNAL_MRAM_RAM_SIZE = 0x00020000;

define exported symbol __EXTERNAL_LCD_BASE = 0x60000000;

define exported symbol __EXTERNAL_LCD_SIZE = 0x1FFFF;

define exported symbol __EXTERNAL_LCD_DC_BASE = 0x60010000;

define exported symbol __INTERNAL_FLASH_BASE = 0x00000000;

define exported symbol __INTERNAL_FLASH_SIZE = 0x00100000;

define exported symbol __INTERNAL_SRAM_BASE = 0x20000000;

define exported symbol __INTERNAL_SRAM_SIZE = 0x00010000;

define exported symbol __INIT = 0x1FFF0000;

define exported symbol __UNCACHED_DATA_END = 0x20020000;

/* The __SRAM_POOL does not exist in fact in the SRAMData target. It should be never referenced

** (runtime check ensures that SRAM pool = system pool) but it can be assigned. The symbol is defined in the vectors.c file.

*/

define exported symbol __INTERNAL_FLEXNVM_BASE = 0;

define exported symbol __INTERNAL_FLEXNVM_SIZE = 0;

define exported symbol __VECTOR_TABLE_ROM_START = 0x70000000;

define exported symbol __VECTOR_TABLE_RAM_START = __ICFEDIT_region_RAM_start__;

define exported symbol __DEFAULT_PROCESSOR_NUMBER = 1;

define exported symbol __DEFAULT_INTERRUPT_STACK_SIZE = 1024;

/* mem_init writes a storeblock_struct at the end of kernel data, max size 32 bytes, so use 0x100 offset */

define exported symbol __BOOT_STACK_ADDRESS = __ICFEDIT_region_RAM_end__ - 0x100;

define exported symbol __KERNEL_DATA_END = __ICFEDIT_region_RAM_end__;

define memory mem with size = 4G;

define region ROM_region = mem:[from __ICFEDIT_region_ROM_start__ to __ICFEDIT_region_ROM_end__];

define region RAM_region = mem:[from __ICFEDIT_region_RAM_start__ to __ICFEDIT_region_RAM_end__];

define block KERNEL_DATA with alignment = 8 { section .kernel_data };

define exported symbol __FLASHX_SECT_SIZE = 0x1000;

define exported symbol __FLASHX_END_ADDR = __INTERNAL_FLASH_BASE + __INTERNAL_FLASH_SIZE;

define block CFMPROTROM with size = 20 { section .cfmconfig };

define block FLASHX_POOL with alignment = __FLASHX_SECT_SIZE { section .flashx };

keep { section .cfmconfig };

keep { section .flashx };

initialize by copy { readwrite };

do not initialize { section .noinit };

do not initialize { section .kernel_data };

do not initialize { section .flashx };

do not initialize { section .cfmconfig };

place at address mem:__ICFEDIT_intvec_start__ { readonly section .intvec, block CFMPROTROM};

place in ROM_region { readonly, last block FLASHX_POOL };

place at address mem:__ICFEDIT_region_RAM_start__ { readwrite section .vectors_ram };

/* each block/segment must be in one line (association to region) because I need kernel data start after other datas */

place in RAM_region { readwrite, last block KERNEL_DATA };

I successed load my code into ext ddr2 ram, but the PC register is not point to the boot.o address while should be 0x70000XXX, then the program is not running.

Did I miss out something need to do?

Please advice.

Thankx

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi ,

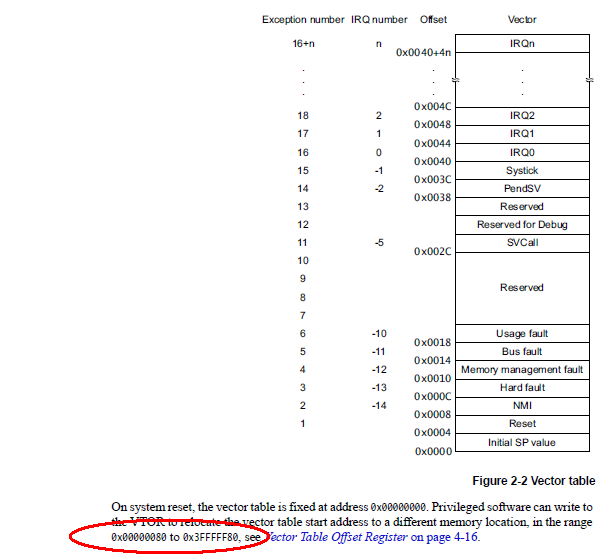

The issue you met is due to the interrupt vector table is out of range. It should be relocated in a address from 0x00000080 to 0x3FFFFF80, but you put it started from 0x70000000. Please kindly refer to the following for details.

You may also refer to DUI0553A_cortex_m4_dgug.pdf for more details, which can be downloaded from www.arm.com.

Hope that helps,

B.R

Kan

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi ,

The issue you met is due to the interrupt vector table is out of range. It should be relocated in a address from 0x00000080 to 0x3FFFFF80, but you put it started from 0x70000000. Please kindly refer to the following for details.

You may also refer to DUI0553A_cortex_m4_dgug.pdf for more details, which can be downloaded from www.arm.com.

Hope that helps,

B.R

Kan

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Li,

This issue have been ignore until now.

Previously I failed to make it run in DDR2 RAM, due to project deadline, I handed-on the project with IntFlash and DDR2data setup.

Now, I have another project using this MK61FX512 and MQX, but my code is larger, so I need to looking into this issue again.

Currently I'm using MQX 4.2 and IAR 7.30, with refer to KINETIS_120MHZ_SC project, I modified the linker file like below:

/*###ICF### Section handled by ICF editor, don't touch! ****/

/*-Editor annotation file-*/

/* IcfEditorFile="$TOOLKIT_DIR$\config\ide\IcfEditor\cortex_v1_0.xml" */

/*-Specials-*/

define symbol __ICFEDIT_intvec_start__ = 0x1fff0000;

/*-Memory Regions-*/

define symbol __ICFEDIT_region_ROM_start__ = 0x08000000;

define symbol __ICFEDIT_region_ROM_end__ = 0x08FFFFFF;

define symbol __ICFEDIT_region_RAM_start__ = 0x71000000;

define symbol __ICFEDIT_region_RAM_end__ = 0x7FFFFFF0;

/*-Sizes-*/

define symbol __ICFEDIT_size_cstack__ = 0;

define symbol __ICFEDIT_size_heap__ = 0;

/**** End of ICF editor section. ###ICF###*/

define exported symbol __EXTERNAL_MRAM_ROM_BASE = 0xA0000000;

define exported symbol __EXTERNAL_MRAM_ROM_SIZE = 0x00000000;

define exported symbol __EXTERNAL_MRAM_RAM_BASE = 0xA0000000;

define exported symbol __EXTERNAL_MRAM_RAM_SIZE = 0x00080000;

define exported symbol __EXTERNAL_DDR2_RAM_BASE = 0x70000000;

define exported symbol __EXTERNAL_DDR2_RAM_SIZE = 0x08000000;

define exported symbol __EXTERNAL_LCD_BASE = 0xA0000000;

define exported symbol __EXTERNAL_LCD_SIZE = 0x1FFFF;

define exported symbol __EXTERNAL_LCD_DC_BASE = 0xA0010000;

define exported symbol __INTERNAL_FLASH_BASE = 0x00000000;

define exported symbol __INTERNAL_FLASH_SIZE = 0x00100000;

define exported symbol __INTERNAL_SRAM_BASE = 0x1FFF1000;

define exported symbol __INTERNAL_SRAM_SIZE = 0x00020000;

define exported symbol __UNCACHED_DATA_END = __ICFEDIT_region_RAM_end__;

define exported symbol __INTERNAL_FLEXNVM_BASE = 0;

define exported symbol __INTERNAL_FLEXNVM_SIZE = 0;

define exported symbol __VECTOR_TABLE_ROM_START = 0x1fff0000;

define exported symbol __VECTOR_TABLE_RAM_START = 0x1fff0000;

define exported symbol __DEFAULT_PROCESSOR_NUMBER = 1;

define exported symbol __DEFAULT_INTERRUPT_STACK_SIZE = 1024;

/* mem_init writes a storeblock_struct at the end of kernel data, max size 32 bytes, so use 0x100 offset */

define exported symbol __BOOT_STACK_ADDRESS = __ICFEDIT_region_RAM_end__ - 0x100;

define exported symbol __KERNEL_DATA_END = __ICFEDIT_region_RAM_end__;

define memory mem with size = 4G;

define region ROM_region = mem:[from __ICFEDIT_region_ROM_start__ to __ICFEDIT_region_ROM_end__];

define region RAM_region = mem:[from __ICFEDIT_region_RAM_start__ to __ICFEDIT_region_RAM_end__];

define block KERNEL_DATA with alignment = 8 { section .kernel_data };

define exported symbol __FLASHX_SECT_SIZE = 0x1000;

define exported symbol __FLASHX_END_ADDR = __INTERNAL_FLASH_BASE + __INTERNAL_FLASH_SIZE;

define block CFMPROTROM with size = 20 { section .cfmconfig };

define block FLASHX_POOL with alignment = __FLASHX_SECT_SIZE { section .flashx };

keep { section .cfmconfig };

keep { section .flashx };

//initialize by copy { readwrite };

initialize manually { readwrite };

initialize manually { section .data};

initialize manually { section .textrw };

do not initialize { section .noinit };

do not initialize { section .kernel_data };

do not initialize { section .flashx };

do not initialize { section .cfmconfig };

place at address mem:__ICFEDIT_intvec_start__ { readonly section .intvec, block CFMPROTROM };

place in ROM_region { readonly, last block FLASHX_POOL };

place at address mem:__INTERNAL_SRAM_BASE {section USB_BDT_Z, section .sram_pool };

//place at address mem:__ICFEDIT_region_RAM_start__ { readwrite section .vectors_ram };

place in ROM_region { readwrite, last block KERNEL_DATA };

Without using flashloader, I can download the ROM_region data, however the VECTOR_TABLE_ROM was not loader into 0x1FFF0000.

Do you know what's wrong?

If possible, can you create a MQX IAR project with successful debugging in DDR2 RAM, because my project due date is kinda near.

Thank you,

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Thank for the reply.

I got it success go to the new boot.o address.

Now solving some initialization problem.

Thank you so much.