- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- K22: SPI with GPIO PCS - All CTAR settings still valid?

K22: SPI with GPIO PCS - All CTAR settings still valid?

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

K22: SPI with GPIO PCS - All CTAR settings still valid?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Device: MK22FN256VLL12.

So I ran out of hardware PCSs for the hardware I'm working on - for both SPI0 and SPI1.

I can see it is possible to use any GPIO as "manual" toggling before setting the PUSHR register and starting the transfer.

My question is: Are custom timings such as ASC and PSC still implemented and used when it is specified in the CTAR, and the specific CTAR is selected in PUSHR - BUT I toggle a GPIO for chip-selection? If so, how does this work, exactly?

If not, what parts of the CTAR applies, when I use a GPIO for chip-selection - surely basics as the SPI mode (CPHA,CPOL) are obeyed?

Thanks a lot.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Troels,

I see your problem that you want to use GPIO as chip select instead of SPI_PCSx.

When the SPI module is designed, the SPI_PCSx had been thought as the chip select to access slave spi in default. Anyway, I think the timing features defined in CTARx is always valid, and the CPHA,CPOL features are also valid.

I think it is okay to use GPIO as chip select to access slave spi module, but you can NOT use FIFO mode, you have to disable FIFO. the SPI0 has 4 deepth FIFO for both receiver and transmitter, the SPI1 does not support FIFO mode itself.

Because FIFO mode is disabled, the SPI master generates the timing only after you write the SPIx_PUSHR register.

This is the sequence of firmware.

1)configure the SPI module and disable FIFO by setting the DIS_TXF in SPIx_MCR register.

2)configure GPIO pin

3)clear GPIO

4)after a programmable delay, write the SPIx_PUSHR, the SPI will generate timing based on your predefined features in CTARx.

5)use interrupt or polling modes, check TCF or RFDF bits in the SPIx_SR to check if the transmitter has finished, if the flag is set, read data, set GPIO, delay some time.

6)repeat (3) operation.

This is my opinion, pls have a try

Hope it can help you.

BR

Xiangjun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Xiangjun Rong,

Thanks for your reply, it is much appreciated.

I already did it the way you also suggested - and it works fine. FIFO is disabled.I was just a bit puzzled by how the various timings that define the edge of SCK compared to PCS can be valid when there SPI module doesn't know when the GPIO toggles compared to when PUSHR is written.

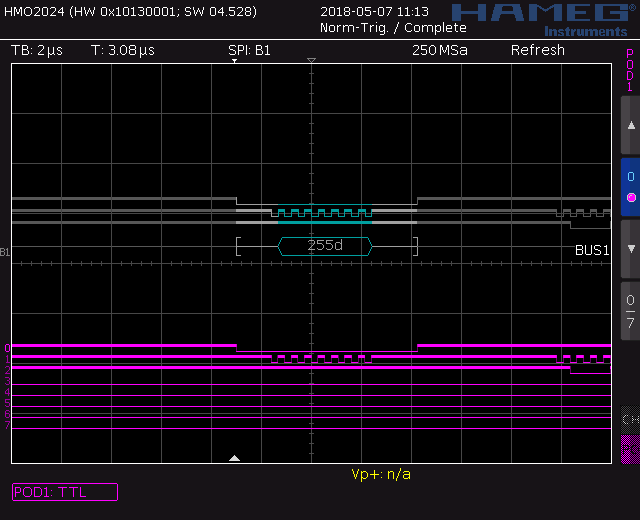

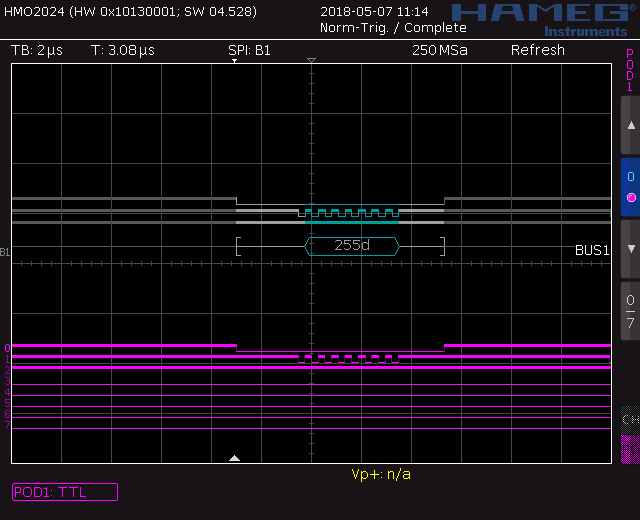

But from my testing, it seems as if the CSSCK setting is obeyed, as illustrated below. Here, I am running the SPI clock at 1.875 MHz, with a CSSCK of 16, 32 and 64. In all instances, the value of 255 is sent from the MCU.

Any changes to the ASC setting are however, ignored. So my interpretation of this is that

the CSSCK timing is with regards to when the PUSHR register is written, and not when the PCS (if used) was de-asserted. By following this logic, it also makes sense that ASC cannot be applied when using a GPIO for CS, since how should it doesn't have any control of the CS?!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Troels,

I think the ASC parameter is valid, the ASC is the delay between the last edge of SCK and the negation of PCS, because the PCS is replaced by GPIO, so you can not observe the ASC effect. The DT is invalid because you do not use FIFO mode.

Hope it can help you

BR

Xiangjun Rong