- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- K10 SRAM size

K10 SRAM size

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

K10 SRAM size

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

I found something that is not OK for me on Kinetis K10.

I'm using a kinetis MK10DX256ZVLQ10 and the manual says that it has 64Kb of SRAM.

In the manual is wrote that that size is the total RAM available.

Due to my linker script error, my application is using 128K from 0x1FFF0000 to 0x2000FFFF.

The thing that is not OKis that the application is working and I don't know if is only lucky or if there is 64Kb x2 block.

As the manual says the SRAM for this microcontroller has to be from 0x1FFF8000 to 20007FFF.

Is it a manual error?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

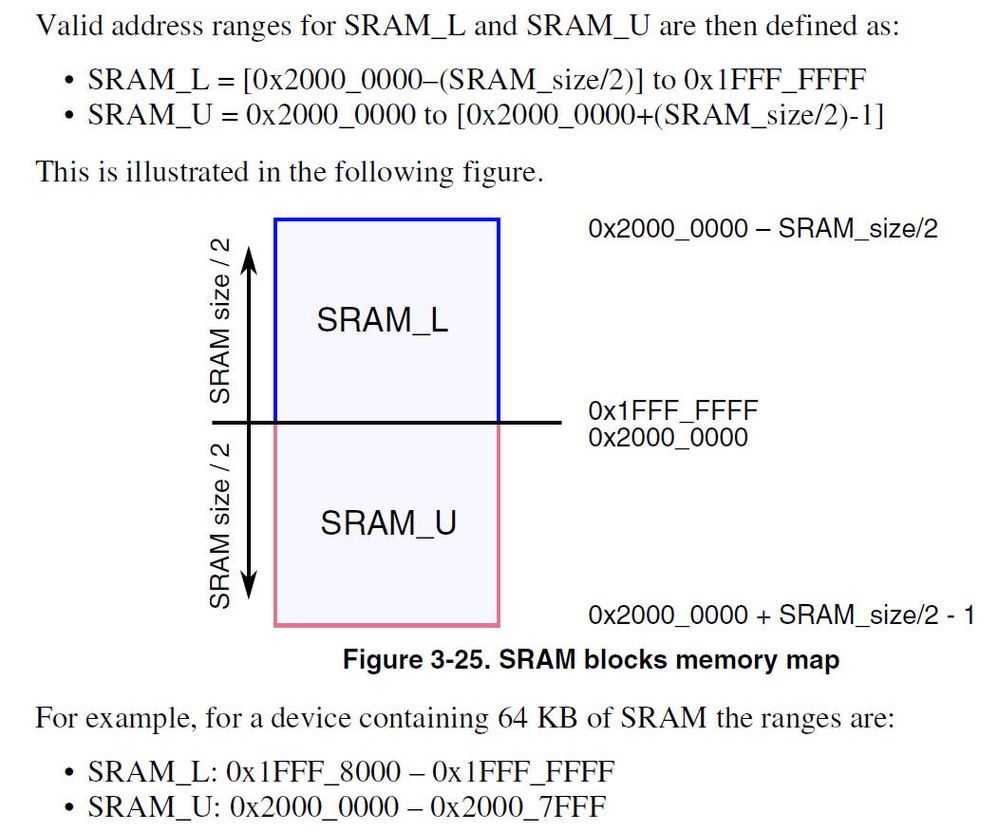

MK10DX256ZVLQ10 SRAM size is 64KB, please refer below picture about SRAM memory map, which should be from from 0x1FFF8000 to 20007FFF.

SRAM_L & SRAM_U split address is fixed to 0x20000000.

Wish it helps.

Best regards,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi guys,

I have a complete knowledge about the memory organization and the memory map of this PCU MK10DX256ZVLQ10.

What I mean is that it's more than one year that I'm using this PCU and I have produced thousand of devices where the firmware works mapping on 128k from 0x1FFF_0000 to 0x2000_0000 as SRAM-L and from 0x2000_FFFF as SRAM-U and it works always correctly.

Moreover, with the debugger I'm able to see all the 128k mapped SRAM. The font of the application are mapped from 0x1FFF_1000 (that are, in theory, out from the 64k available).

So my question is...is it possible that this PCU is always equipped with 128k SRAM because of freescale does not want to produce two different silicons, providing guarantee just on the declared 64 SRAM (as in other case INTEL did with Pentium II cache)?

Thank you,

Luca

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

At this moment there is not any register of erratas related to this situation, I suggest you to enter a Service Request and ask for any change or errata for you specific part marking device.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

I recommend doing the following test:

Using a debugger, write a value to the address 0x1fff0000 - if it reads back the same value there is SRAM there

Check the address 0x1fff8000 - if the value follows the value that you wrote to 0x1fff0000 it is being mirrored and there is 64k (but being written/read at different locations)

You can repeat at 0x20007ff0 and 0x2000fff0 (for example).

Normally there will be an access error generated when reading/writing outside fo the SRAM area but maybe there is a difference in your device

If you can write/read without mirroring effect you really have 128k SRAM.

If mirroring is taking place the code will probably still be able to run as long as it doesn't use more that 64k (since its static variables are probably starting at 0x1fff0000 and its stack using the 0x2000ffff area (which mirror to 0x1fff8000 and 0x20007fff respecively and so don't corrupt each other).

Regards

Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I already did that test.

I have some variables placed at 0x1FFF0400. Are fonts and I know that works because of chars are showed wll on display.

Than, cna be the manual error or is the block of 512 and 256 CPUs the same and Freescale doesn't block the access to the not declared SRAM?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Maybe the device has the wrong part number stamped on it?

Check the register SIM_SOPT1 (RAM_SIZE) to see whether that agrees.

Since you probably chose the part with 64k because you won't need more I would just set the linker script up for 64k and then it doesn't matter.

Regards

Mark