- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- 通用微控制器

- :

- Kinetis微控制器

- :

- Estimating DMA controller load

Estimating DMA controller load

Estimating DMA controller load

I'm making fairly heavy use of DMA in a project, considerably more than I've used in any previous project. I have high speed (>= 1 mbps) UART traffic, I2S, DAC and ADC samples, and probably SPI a little later.

I'm curious if there are any good tools or techniques for keeping an eye on how busy the DMA controller is, and ideally also how much load is hitting the bus.

The only idea I've come up with so far would be to set up a channel with the lowest possible priority to send alternating 1s and 0s to a GPIO, where it could be monitored with a logic analyzer, the idea being that any gaps in the pattern would represent times the DMA controller was busy with higher-priority requests.

Is that reasonable? Are there other ways to approach it? I've done a little searching and haven't come up with anything, but I may not be using the right search terms.

Thanks,

Scott

Hi Scott,

I think your way sounds reasonable.

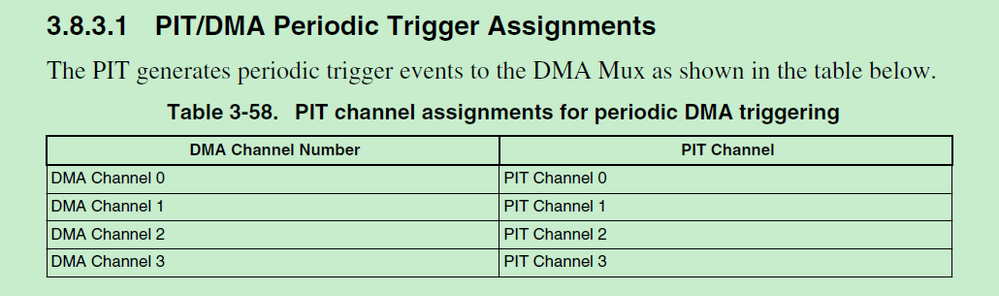

It also could using a PIT to periodic trigger the DMA as eDMA working pulse shows:

The DMA transfer could toggle a GPIO pin.

Customer could short the PIT period interval to check if the eDMA engineer could response the trigger.

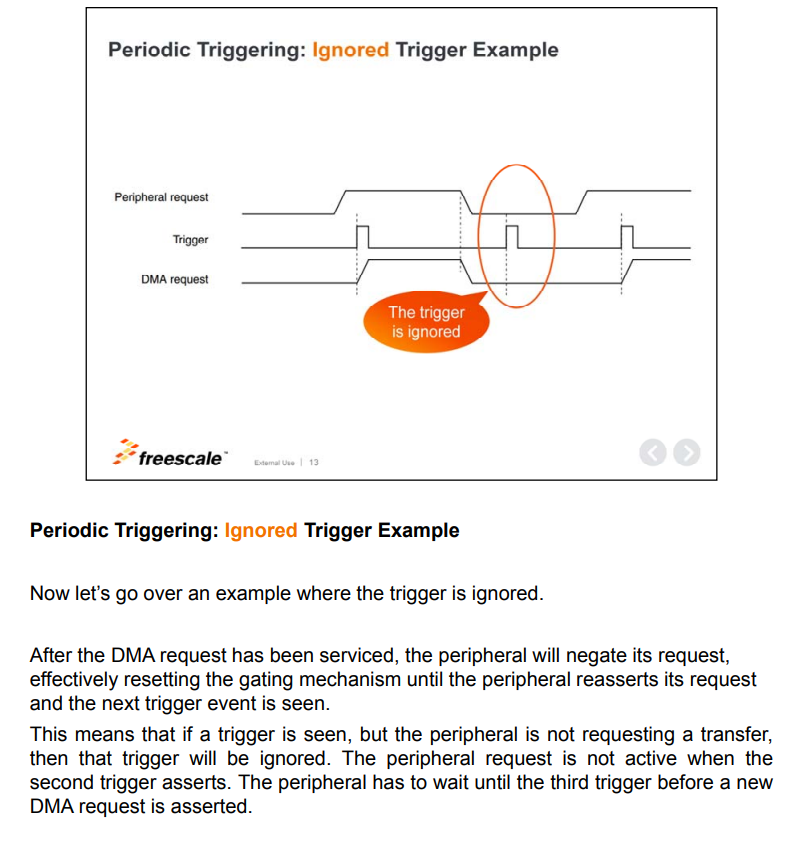

If the eDMA with heavy load, the periodic trigger will be ignored.

More detailed info, please check below picture:

I attached a PIT periodic trigger DMA example for your reference.

Thank you for the attention.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------